US008555370B2

# (12) United States Patent Ellis

## (10) Patent No.: US 8,555,370 B2 (45) Date of Patent: \*Oct. 8, 2013

## (54) MICROCHIPS WITH AN INTERNAL HARDWARE FIREWALL

(76) Inventor: Frampton E Ellis, Jasper, FL (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

This patent is subject to a terminal disclaimer.

(21) Appl. No.: 13/594,614

(22) Filed: Aug. 24, 2012

(65) **Prior Publication Data**

US 2012/0324563 A1 Dec. 20, 2012

### Related U.S. Application Data

Continuation of application No. 12/164,661, filed on Jun. 30, 2008, now Pat. No. 8,332,924, which is a division of application No. 10/684,657, filed on Oct. 2003, now abandoned, which is a continuation-in-part of application No. 09/935,779, filed on Aug. 24, 2001, now Pat. No. 7,506,020, and a continuation-in-part of application PCT/US02/29227, filed on Sep. 16, 2002, which is a continuation-in-part of application No. 09/571,558, filed on May 16, 2000, now Pat. No. 7,035,906, which is a continuation-in-part of application No. 09/315,026, filed on May 20, 1999, now Pat. No. 7,024,449, which is a continuation-in-part of application No. 09/213,875, filed on May 17, 1999, now Pat. No. 6,725,250, which is a continuation-in-part of application No. 09/085,755, filed on May 27, 1998, now Pat. No. 7,634,529, said application No. 09/571,558 is a continuation-in-part of application No. 09/315,026, and a continuation-in-part application No. 09/085,755, and continuation-in-part of application No. 09/213,875, application No. 09/315,026, which is a continuation-in-part of application No. 09/213,875, filed on Dec. 17, 1998, now Pat. No. 6,725,250, which

is a continuation-in-part of application No. PCT/US97/21812, filed on Nov. 28, 1997, which is a continuation-in-part of application No. PCT/US98/27058, filed on Dec. 17, 1998, said application No. 09/213,875 is a continuation-in-part of application No. 08/980,058, filed on Nov. 26, 1997, now Pat. No. 6,732,141, which is a continuation-in-part of application No. 09/085,755.

Provisional application No. 60/418,177, filed on Oct. 15, 2002, provisional application No. 60/323,701, filed on Sep. 21, 2001, provisional application No. 60/322,474, filed on Sep. 17, 2001, provisional application No. 60/227,660, filed on Aug. 25, 2000, provisional application No. 60/308,826, filed on Aug. 1, 2001, provisional application No. 60/135,851, filed on May 24, 1999, provisional application No. 60/135,852, filed on May 24, 1999, provisional application No. 60/136,759, filed on May 28, 1999, provisional application No. 60/086,588, filed on May 22, 1998, provisional application No. 60/086,516, filed on May 22, 1998, provisional application No. 60/086,948, filed on May 27, 1998, provisional application No. 60/087,587, filed on Jun. 1, 1998, provisional application No. 60/088,459, filed on Jun. 8, 1998, provisional application No. 60/134,552, filed on May 17, 1999, provisional application No. 60/086,366, filed on Dec. 19, 1997, provisional application No. 60/066,313, filed on Nov. 21, 1997, provisional application No. 60/066,415, filed on Nov. 24, 1998, provisional application No. 60/031,855, filed on Nov. 29, 1996, provisional application No. 60/032,207, filed on Dec. 2, 1996, provisional application No. 60/033,871, filed on Dec. 20, 1996.

(51) **Int. Cl. G06F 9/00** (2006.01) **G06F 1/24** (2006.01) **H04L 29/06** (2006.01)

(58) **Field of Classification Search**USPC ............. 726/11, 12, 13, 14; 713/100, 151, 153,

See application file for complete search history.

### US 8,555,370 B2

Page 2

| (56)                         | References Cited                             |        | 5,680,461<br>5,680,548 |    |                  | McManis<br>Trugman                 |

|------------------------------|----------------------------------------------|--------|------------------------|----|------------------|------------------------------------|

| U.S.                         | PATENT DOCUMENTS                             |        | 5,696,902              | A  | 12/1997          | Leclercq et al.                    |

|                              | 44(40=0 = 1.4                                |        | 5,699,528              |    | 12/1997          |                                    |

| 3,539,876 A<br>3,835,530 A   | 11/1970 Feinberg et al.<br>9/1974 Kilby      |        | 5,701,507<br>5,710,884 |    |                  | Bonneau, Jr. et al.<br>Dedrick     |

| 4,245,306 A                  | 1/1981 Besemer et al.                        |        | 5,734,913              |    | 3/1998           | Iwamura et al.                     |

| 4,276,594 A                  | 6/1981 Morley                                |        | 5,748,489              |    |                  | Beatty et al.                      |

| 4,278,837 A                  | 7/1981 Best                                  |        | 5,752,067<br>5,754,766 |    |                  | Wilkinson et al.<br>Shaw et al.    |

| 4,467,400 A<br>4,489,397 A   | 8/1984 Stopper<br>12/1984 Lee                |        | 5,758,077              |    |                  | Danahy et al.                      |

| 4,703,436 A                  | 10/1987 Varshney                             |        | 5,758,345              | A  | 5/1998           | Wang                               |

| 4,736,317 A                  | 4/1988 Hu et al.                             |        | 5,761,507              |    | 6/1998           |                                    |

| 4,747,139 A                  | 5/1988 Taaffe                                |        | 5,764,889<br>5,774,337 |    |                  | Ault et al. Lee et al.             |

| 4,827,508 A<br>4,855,903 A   | 5/1989 Shear<br>8/1989 Carleton et al.       |        | 5,774,668              |    |                  | Choquier et al.                    |

| 4,893,174 A                  | 1/1990 Yamada et al.                         |        | 5,774,721              |    |                  | Robinson                           |

| 4,907,228 A                  | 3/1990 Bruckert et al.                       |        | 5,784,551              |    |                  | De Leva et al.<br>Reneris          |

| 4,918,596 A                  | 4/1990 Nakano                                |        | 5,784,628<br>5,790,431 |    |                  | Ahrens, Jr. et al.                 |

| 4,969,092 A<br>5,025,369 A   | 11/1990 Shorter<br>6/1991 Schwartz           |        | 5,793,968              |    |                  | Gregerson et al.                   |

| 5,031,089 A                  | 7/1991 Liu et al.                            |        | 5,794,059              |    |                  | Barker et al.                      |

| 5,068,780 A                  | 11/1991 Bruckert et al.                      |        | 5,802,320<br>5,809,190 |    | 9/1998<br>9/1998 | Baehr et al.                       |

| 5,103,393 A<br>5,109,329 A   | 4/1992 Harris et al.<br>4/1992 Strelioff     |        | 5,815,665              |    |                  | Teper et al.                       |

| 5,109,512 A                  | 4/1992 Bahr et al.                           |        | 5,815,793              | A  |                  | Ferguson                           |

| 5,136,708 A                  | 8/1992 LaPourtre et al.                      |        | 5,826,014              | A  | 10/1998          | Coley et al.                       |

| 5,155,808 A                  | 10/1992 Shimizu                              |        | 5,826,029 5,828,833    |    |                  | Gore et al                         |

| 5,195,031 A<br>5,212,780 A   | 3/1993 Ordish<br>5/1993 Padgaonkar et al.    |        | 5,835,726              |    |                  | Shwed et al.                       |

| 5,214,657 A                  | 5/1993 Farnworth et al.                      |        | 5,838,436              | A  | 11/1998          | Hotaling et al.                    |

| 5,237,507 A                  | 8/1993 Chasek                                |        | 5,838,542              |    |                  | Nelson et al.                      |

| 5,260,943 A                  | 11/1993 Comroe et al.                        |        | 5,843,799<br>5,844,594 |    |                  | Hsu et al.<br>Ferguson             |

| 5,282,272 A<br>5,283,819 A   | 1/1994 Guy et al.<br>2/1994 Glick et al.     |        | 5,845,074              |    | 12/1998          |                                    |

| 5,291,494 A                  | 3/1994 Bruckert et al.                       |        | 5,850,449              |    |                  | McManis                            |

| 5,291,502 A                  | 3/1994 Pezeshki et al.                       |        | 5,861,817              |    |                  | Palmer et al.                      |

| 5,291,505 A                  | 3/1994 Nielsen                               |        | 5,862,357<br>5,864,738 |    |                  | Hagersten et al.<br>Kessler et al. |

| 5,341,477 A<br>5,349,682 A   | 8/1994 Pitkin et al.<br>9/1994 Rosenberry    |        | 5,870,721              |    | 2/1999           |                                    |

| 5,357,404 A                  | 10/1994 Bright et al.                        |        | 5,872,987              |    |                  | Wade et al.                        |

| 5,357,632 A                  | 10/1994 Pian et al.                          |        | 5,881,284<br>5,889,989 |    | 3/1999           | Robertazzi et al.                  |

| 5,361,362 A<br>5,381,534 A   | 11/1994 Benkeser et al.<br>1/1995 Shi        |        | 5,896,499              |    |                  | McKelvey                           |

| 5,388,211 A                  | 2/1995 Hornbuckle                            |        | 5,905,429              | A  | 5/1999           | Hornstein et al.                   |

| 5,392,400 A                  | 2/1995 Berkowitz et al.                      |        | 5,909,052              |    |                  | Ohta et al.                        |

| 5,410,651 A                  | 4/1995 Sekizawa et al.                       |        | 5,909,681<br>5,917,629 |    |                  | Passera et al. Hortensius et al.   |

| 5,426,741 A<br>5,428,783 A   | 6/1995 Butts, Jr. et al.<br>6/1995 Lake      |        | 5,919,247              |    |                  | Van Hoff et al.                    |

| 5,434,998 A *                | 7/1995 Akai et al                            | 714/11 | 5,930,511              |    |                  | Hinsley                            |

| 5,446,843 A                  | 8/1995 Fucito et al.                         |        | 5,943,421              |    | 404000           | Grabon                             |

| 5,457,797 A<br>5,475,606 A   | 10/1995 Butterworth et al.                   |        | 5,964,832<br>5,978,829 |    | 10/1999          | Chung et al.                       |

| 5,497,465 A                  | 12/1995 Muyshondt et al. 3/1996 Chin et al.  |        | 6,003,133              | A  |                  | Moughanni et al.                   |

| 5,515,511 A                  | 5/1996 Nguyen et al.                         |        | 6,052,555              |    |                  | Ferguson                           |

| 5,522,070 A                  | 5/1996 Sumimoto                              |        | 6,065,118<br>6,067,082 |    | 5/2000           | Bull et al.                        |

| 5,530,949 A *<br>5,535,408 A | 6/1996 Koda et al                            |        | 6,073,209              |    |                  | Bergsten                           |

| 5,546,594 A                  | 8/1996 Wazumi                                |        | 6,078,733              | A  | 6/2000           | Osborne                            |

| 5,550,984 A                  | 8/1996 Gelb                                  |        | 6,093,933              |    |                  | Farnworth et al.                   |

| 5,568,375 A                  | 10/1996 Rausch                               |        | 6,098,091<br>6,112,225 |    | 8/2000           | Kraft et al.                       |

| 5,570,270 A<br>5,572,643 A   | 10/1996 Naedel et al.<br>11/1996 Judson      |        | 6,112,243              |    |                  | Downs et al.                       |

| 5,576,554 A                  | 11/1996 Hsu                                  |        | 6,115,698              |    |                  | Tuck et al.                        |

| 5,586,121 A                  | 12/1996 Moura et al.                         |        | 6,167,428              |    | 12/2000          | Ellis<br>Diamant et al.            |

| 5,587,928 A                  | 12/1996 Jones et al.                         |        | 6,202,153<br>6,208,634 |    |                  | Boulos et al.                      |

| 5,588,003 A<br>5,590,284 A   | 12/1996 Ohba et al.<br>12/1996 Crosetto      |        | 6,219,627              |    |                  | Bonneau et al.                     |

| 5,592,376 A                  | 1/1997 Hodroff                               |        | 6,268,788              |    | 7/2001           |                                    |

| 5,592,632 A                  | 1/1997 Leung et al.                          |        | 6,287,949              |    |                  | Mori et al.                        |

| 5,594,491 A                  | 1/1997 Hodge et al.                          |        | 6,326,245<br>6,366,472 |    |                  | Farnworth et al. Alina et al.      |

| 5,600,597 A<br>5,604,882 A   | 2/1997 Kean et al.<br>2/1997 Hoover et al.   |        | 6,440,775              |    |                  | Khoury                             |

| 5,606,615 A                  | 2/1997 Lapointe et al.                       |        | 6,645,832              | B2 |                  | Kim et al.                         |

| 5,608,448 A                  | 3/1997 Smoral et al.                         |        | 6,725,250              | B1 |                  | Ellis, III                         |

| 5,615,127 A                  | 3/1997 Beatty et al.                         |        | 6,732,141              |    | 5/2004           |                                    |

| 5,627,879 A<br>5,666,484 A   | 5/1997 Russell et al.<br>9/1997 Orimo et al. |        | 6,772,347<br>6,797,545 |    |                  | Xie et al.<br>Farnworth et al.     |

| 5,678,028 A                  | 10/1997 Bershteyn et al.                     |        | 6,950,947              |    |                  | Purtell et al.                     |

|                              | •                                            |        |                        |    |                  |                                    |

### US 8,555,370 B2

Page 3

|              |               |                  | ****                                                                 |

|--------------|---------------|------------------|----------------------------------------------------------------------|

| 7,024,449    |               | Ellis, III       | WO WO 94/01964 1/1994                                                |

| 7,035,906    |               | Ellis, III       | WO WO 95/01060 1/1995                                                |

| 7,047,275    |               |                  | WO WO 98/26366 6/1998                                                |

| 7,148,565    | 5 B2 12/2006  | Kim et al.       | WO WO 99/04561 1/1999                                                |

| 7,161,175    | 5 B2 1/2007   | Shau             | WO WO 99/32972 7/1999                                                |

| 7,412,588    | 8 B2 8/2008   | Georgiou et al.  | WO WO 2011/094616 8/2011                                             |

| 7,467,406    |               | Cox et al.       | WO WO 2011/103299 8/2011                                             |

| 7,506,020    |               |                  |                                                                      |

| 7,562,211    |               | Paya et al.      | OTHER PUBLICATIONS                                                   |

|              |               | Ellis, III       |                                                                      |

| 7,606,854    |               |                  | Fengjing Shao et al., "A new secure architecture of network computer |

| 7,634,529    |               | Ellis, III       | based on single CPU and Dual Bus" Fifth IEEE International Sym-      |

| 7,805,756    |               |                  | posium on Embedded Computing, pp. 309-314 (2008).                    |

| 7,814,233    |               |                  | Tiedong Wang et al., "A Hardware implement of Bus Bridge Based       |

| 7,840,997    |               | Shevchenko       |                                                                      |

| 7,908,650    | ) B2 3/2011   | Ellis            | on Single CPU and Dual Bus", 2008 International Symposium on         |

| 7,926,097    | 7 B2 4/2011   | Ellis            | Computer Science and Computational Technology, pp. 17-20 (2008).     |

| 7,984,301    | l B2 7/2011   | Kaabouch et al.  | Famatech "Radmin V3.0, User Manuel", Jun. 3, 2007 (203 pages).       |

| 8,010,789    | B2 8/2011     | Witchey          | Connect One, iChip CO2064/CO2128/CO2144, 2011 (64 pages).            |

| 8,125,796    |               |                  |                                                                      |

| 8,164,170    |               |                  | File History of U.S. Appl. No. 12/829,120, electronically captured   |

| 8,171,537    |               |                  | from PAIR on May 16, 2013 for Oct. 11, 2012 to May 16, 2013.         |

|              |               |                  | File History of U.S. Appl. No. 13/016,149, electronically captured   |

| 8,209,373    |               |                  | from PAIR on May 16, 2013 for Oct. 11, 2012 to May 16, 2013.         |

| 8,255,986    |               |                  |                                                                      |

| 8,291,485    |               |                  | File History of U.S. Appl. No. 13/018,089, electronically captured   |

| 8,312,529    |               |                  | from PAIR on May 16, 2013 for Oct. 11, 2012 to May 16, 2013.         |

| 8,378,474    |               |                  | File History of U.S. Appl. No. 13/180,164, electronically captured   |

| 2001/0011294 |               | Ellis, III       | from PAIR on May 16, 2013 for Oct. 11, 2012 to May 16, 2013.         |

| 2001/0013049 | 9 A1 8/2001   | Ellis, III       | File History of U.S. Appl. No. 13/240,842, electronically captured   |

| 2001/0046119 |               | Hamano et al.    |                                                                      |

| 2001/0054159 |               | Hoshino          | from PAIR on May 16, 2013 for Oct. 11, 2012 to May 16, 2013.         |

| 2002/0059392 |               | Ellis, III       | File History of U.S. Appl. No. 13/283,274, electronically captured   |

| 2002/0087886 |               |                  | from PAIR on May 16, 2013 for Oct. 11, 2012 to May 16, 2013.         |

| 2004/0073603 |               |                  | File History of U.S. Appl. No. 13/495,867, electronically captured   |

|              |               |                  | from PAIR on May 16, 2013 for Oct. 11, 2012 to May 16, 2013.         |

| 2004/0098621 |               | Raymond          |                                                                      |

| 2004/0158744 |               | Deng et al.      | File History of U.S. Appl. No. 13/599,484, electronically captured   |

| 2004/0162992 |               | Sami et al.      | from PAIR on May 16, 2013 for Oct. 11, 2012 to May 16, 2013.         |

| 2004/0215931 |               |                  | File History of U.S. Appl. No. 13/328,697, electronically captured   |

| 2005/0138169 | 9 A1 6/2005   | Bahr             | from PAIR on May 16, 2013.                                           |

| 2005/0180095 | 5 A1 8/2005   | Ellis            | File History of U.S. Appl. No. 13/014,201, electronically captured   |

| 2006/0075001 | l A1 4/2006   | Canning et al.   | from PAIR on May 16, 2013.                                           |

| 2006/0095497 |               | Ellis            |                                                                      |

| 2006/0177226 |               |                  | File History of U.S. Appl. No. 13/016,527, electronically captured   |

| 2006/0190565 |               |                  | from PAIR on May 16, 2013.                                           |

| 2006/0248749 |               |                  | File History of U.S. Appl. No. 12/292,769, electronically captured   |

| 2007/0162974 |               | Speidel          | from PAIR on May 16, 2013.                                           |

|              |               |                  | File History of U.S. Appl. No. 12/292,553, electronically captured   |

| 2007/0196948 |               | Trezza           | from PAIR on May 16, 2013.                                           |

| 2007/0300305 |               | Gonsalves et al. |                                                                      |

| 2008/0083976 |               | Haba et al.      | File History of U.S. Appl. No. 13/426,133, electronically captured   |

| 2008/0134290 |               | Olsson           | from PAIR on May 16, 2013.                                           |

| 2009/0026524 |               | Kreupl et al.    | File History of U.S. Appl. No. 13/398,403, electronically captured   |

| 2009/0031412 |               | Ellis            | from PAIR on May 16, 2013.                                           |

| 2009/0168329 | 9 A1 7/2009   | Ellis            | File History of U.S. Appl. No. 13/555,750, electronically captured   |

| 2009/0200661 | I A1 8/2009   | Ellis            |                                                                      |

| 2009/0254986 | 5 A1 10/2009  | Harris et al.    | from PAIR on May 16, 2013.                                           |

| 2009/0282092 |               |                  | File History of U.S. Appl. No. 13/404,888, electronically captured   |

| 2010/0011083 |               |                  | from PAIR on May 16, 2013.                                           |

| 2010/0011803 |               | Warnecker et al. | U.S. Appl. No. 09/315,026, filed May 20, 2002.                       |

| 2011/0004930 |               | Ellis            | U.S. Appl. No. 09/571,558, filed May 16, 2000.                       |

| 2011/0004931 |               | Ellis            | U.S. Appl. No. 09/669,730, filed Sep. 26, 2000.                      |

| 2011/0004931 |               |                  | U.S. Appl. No. 09/320,660, filed May 27, 1999.                       |

|              |               | Ellia            |                                                                      |

| 2011/0231926 |               |                  | U.S. Appl. No. 09/213,875, filed Dec. 17, 1998.                      |

| 2011/0271339 |               |                  | U.S. Appl. No. 13/495,867, filed Jun. 13, 2012.                      |

| 2012/0030747 | / A1 2/2012   | Ellis, III       | U.S. Appl. No. 13/594,614, filed Aug. 24, 2012.                      |

| 2012/0030748 |               | Ellis, III       | U.S. Appl. No. 13/599,484, filed Aug. 30 2012.                       |

| 2012/0042372 |               |                  | U.S. Appl. No. 13/783,351, filed Mar. 3, 2013.                       |

| 2012/0054849 |               | Ellis, III       | U.S. Appl. No. 13/761,126, filed Feb. 6, 2013.                       |

| 2012/0096537 |               |                  |                                                                      |

| 2012/0155002 |               | Ellis            | U.S. Appl. No. 13/768,582, filed Feb. 15, 2013.                      |

| 2012/0175752 |               | Ellis            | U.S. Appl. No. 13/815,814, filed Mar. 15, 2013.                      |

| 2012/0311690 |               |                  | U.S. Appl. No. 13/769,292, filed Feb. 16, 2013.                      |

|              |               |                  | Litzkow, et al., "Condor—A Hunter of Idle Workstations", 1988        |

| 2012/0317634 | T /A1 12/2012 | LIII3            | IEEE, pp. 104-111.                                                   |

|              |               |                  | Theimer, et al., "Finding idle Machines in a Workstation-Based Dis-  |

| FO           | OREIGN PATI   | ENT DOCUMENTS    |                                                                      |

|              |               |                  | tributed System", IEEE Transactons on Software Engineering, Nov.     |

| DE           | 40 08 335     | 9/1991           | 1989, vol. 15, No. 11, pp. 1444-1458.                                |

| EP           | 0 647 052     | 4/1995           | Brown et al., Special Edition Using Netscape TM 2 Second Edition,    |

| EP           | 0 840216      | 5/1998           | Que Corporation, 1995 Ch. 1-2.                                       |

| EP           | 0 853 279     | 7/1998           | Gilder, "Angst and Awe on the Internet by George Gilder", Forbes     |

| EP           | 1 164 766     | 12/2011          | ASAP, Dec. 4, 1995.                                                  |

|              | 1 10 1 700    | 12/2011          | 12011, 200, 1, 1999,                                                 |

Tandiary, et al., "Batrun: Utilizing Idle Workstations for Large-scale Computing", Summer 1996, pp. 41-48.

Brisbin, "Shopping for Internet Access", MacUser, Dec. 1994, v. 10, p. 133(2).

Gilder, "The Bandwidth Tidal Wave", Forbes ASAP, Dec. 5, 1994. N/A, "Special Report—Wonder Chips", Business Week, Jul. 4, 1994. N/A, "Supercomputers Divide and Conquer", The Economist, Dec. 14, 1996.

N/A, "Cyber View World Widgets", Scientific American, May 1997, p. 48

Gibbs, "Bandwidth, Unlimited", Scientific American, Jan. 1997, p. 41

Markoff, "A New Standard to Govern PC's with Multiple Chips, Work Stations Mimicking Supercomputers", The New York Times, Oct 28, 1997

N/A, "Aliens on your desktop", The Economist, Apr. 18, 1998, p. 78. Fox et al., Petaops and Exaops: Supercomputing on the Web, "IEEE Internet Computing", vol. 1 No. 2 Mar.-Apr. 1997, pp. 38-46.

Dincer et al., Building a World-Wide Virtual Machine Based on Web and HPCC Technologies, "Student Technical Papers"; http://www.supercomp.org/sc96/proceedings/SC96PROC/DINCER/INDEX. HTM, pp. 1-18 (1996).

Hobbs et al., A Remote Process Creation and Execution Facility Supporting Parallel Execution on Distributed Systems, "IEEE 1996", pp. 92-99.

Boku et al., The Architecture of Massively Parallel Processor CP-PACS, "IEEE 1997", pp. 31-40.

Choi et al., A Diagnostic Network for Massively Parallel Processing Systems, "IEEE 1994", pp. 348-353.

Bellovin et al., Network Firewalls, "IEEE Communications Magazine 1994", pp. 50-57.

Weiyi et al., "Java-to-Go—Itinerative Computing Using Java", Sep. 10, 1996 http://ptolemy.eecs.berkeley.edu/dgm/javatools/java-to-go/

Sullivan et al., "A New Major SETI Project Based on Project Serendip Data and 100,000 Personal Computers". http://setiathome.ss/berkeley.edu/woody\_paper.htm/: (1997).

"Ein-Chip-Firewall", Elektroniknet Top News, XP-002164257; Mar. 31, 1999.

"Means for Implementing Optical Interconnections for Parallel Processors", IBM Technical Disclosure Bulletin, Apr. 1991, vol. 33, No. 11, pp. 56-58, XP 000110310.

Alexandrov et al., "SuperWeb: Research Issues in Java-Based Global Computing", Concurrency, vol. 9, No. 6, Jun. 1997, pp. 535-553.

Baratloo et al., "Charlotte: Metacomputing on the Web", 9th International Conference on Parallel and Distributed Computing Systems (PDCS), 1996, pp. 1-8.

Bevinakoppa et al., "Digital Image Compression on a Network of Transputers", Proc. of 5th Australian Transputer & OCCAM User Group Conference, IOS Press, Amsterdam, pp. 25-32; Nov. 4, 1992. Blumofe, R. et al., "Scheduling Large-Scale Parallel Computations on Networks of Workstations", Proc. of the 3rd IEEE Int'l Sump on High Performance Distributed Computing, pp. 96-105, Aug. 1994. Fields, Scott, "Hunting for Wasted Computing Power—New Software for Computing Networks Plus Idle PC's to Work", 1993 University of Wisconsin—Madison. Internet: http://www.cs.wise.edu/condor/doc/Wiseidea.html.

Brecht et al., "ParaWeb: Towards World-Wide Supercomputing", Proceedings of the Seventh AcM SIGOPS European Workshop, Sep. 1996, 8 pgs.

Capello et al., "Market-Based Massively Parallel Internet Computing", Proceedings Third Working Conference on Massively Parallel Programming Models, 1998, pp. 118-129.

Celenk, M. et al., "Parallel Task Execution in LANs and Performance Analysis", Proc. of the 1995 IEEE 14th Annual Int'l Phoenix Conf. on Computers and Communications, pp. 423-429, Mar. 1995.

Chen, C. et al., "The DBC: Processing Scientific Data Over the Internet", Proc. of the 16th Int'l Conf. on Distributed Computing Systems, pp. 673-679, May 1996.

Clark, H. et al., "DAWGS—A Distributed Computer Server Utilizing Idle Workstations", Proc. of the 5th Distributed Memory Computing Conf., IEEE, pp. 732-741, Apr. 1990.

Fogg, C., "Survey of Software and Hardware VLC Architectures", SPIE, vol. 2186, Image and Video Compression (1994), pp. 29-37. Fox et al., "Towards Web/Java based High Performance Distributed Computing—an Evolving Virtual Machine", as presented at 5th

Computing—an Evolving Virtual Machine", as presented at 5th IEEE Int'l Symposium on High Performance Distributed Computing, Aug. 6-9, 1996, 86 pages.

Fox. E., "Advances in Interactive Digital Multimedia Systems", Computer, Oct. 1991, pp. 9-21.

Gemmell, et al., "Multimedia Storage Servers: a Tutorial", Computer, May 1995, pp. 40-49.

Hayes, "Computing Science: Collective Wisdom", American Scientist, Mar.-Apr. 1998, pp. 1-8.

Kim, B., "ATM Network: Goals and Challenges", Communications of the ACM, Feb. 1995, vol. 38, No. 2, pp. 39-44, 109.

Kremien, O., "Buying and Selling Computational Power Over the Network", Proc. of the 4th Int'l Conf. on Computer Communications and Networks, IEEE, pp. 616-619, Sep. 1995.

Lindley, C., "JPEG-Like Image Compression, Part 2", Dr. Dobb's Journal, Aug. 1995, pp. 62-66, 102-105.

Lindley, C., "JPEG-Like Image Compression, Part 1", Dr. Dobb's Journal, Jul. 1995, pp. 50-58, 101-102.

Morris, J. et al., "Fault Tolerant Networks of Workstations", Proc. of the 3rd Int'l, Conf. on High Performance Computing, IEEE, pp. 271-276, Dec. 1996.

Nass, R., "Hardware-software combo could simplify MPEG real-time video compression", Electronic Design, May 3, 1993, p. 36.

Nowatzyk et al., "Are Crossbars Really Dead? The Case for Optical Multiprocessor Interconnect Systems", Proceedings of the Annual Symposium on Computer Architecture, ACM, vol. 22, Jun. 1995, pp. 106-115, XP 000687800.

Ozer, "Digital Video: Shot by Shot", PC Magazine, Apr. 11, 1995, pp. 104-107, 110.

Ozer, J., "Why MPEG is Hot", PC Magazine, Apr. 11, 1995, pp. 130-131.

Plotkin, "The Digital Compression Facility—A Solution to Today's Compression Needs", 1994 IEEE, pp. 445-449.

Qiao et al., "Time-Division Optical Communications in Multiprocessor Arrays", ACM, 1991, pp. 644-653, XP 000337522.

Rincon et al., "The Changing Landscape of System-on-a-chip Design", MicroNews, Third Quarter 1999, www.chips.ibm.com/micronews/vol5\_no3/rincon.html, pp. 1-10, vol. 5, No. 3.

Sachs, M. et al., "LAN and I/O Convergence: A Survey of the Issues", Computer, Dec. 1994, pp. 24-32.

Sakano, et al., "A Three-Dimensional Mesh Multiprocessor System Using Board-to-Board Free-Space Optical Interconnects: COSINE-III", IEEE, 1993, pp. 278-283, XP 000463415.

Schroeder, E., "New Offerings Buoy MPEG as Video Standard", Desktop Computing, PC Week, May 8, 1995, pp. 1 and 29.

Shen et al., "A Parallel Implementation of an MPEG1 Encoder: Faster than Real-Time?", Proc. of SPIE Conf. on Digital Video Compression, San Jose, CA, Feb. 1995.

McHenry et al., "An FPGA-Based Coprocessor for ATM Firewalls", Field-Programmable Custom Computing Machines 1997, Apr. 16-18, 1997, pp. 30-39, XP-002157218.

Shiuan, J. et al., "Client-Server Based Ray-Tracer Using ASTRA: An Asynchronous RPC Mechanism", Computer Communications, vol. 19, No. 5, pp. 445-455, May 1996.

Szabo, B. et al., "Design Considerations for JPEG Video and Synchronized Audio in a Unix Workstation Environment", USENIX-Summer '91, pp. 353-368.

Vetter, R., "ATM Concepts, Architectures, and Protocols, Communications of the ACM", Feb. 1995; vol. 38, No. 2, pp. 30-38, 109.

Vetter, R. et al., "Issues and Challenges in ATM Networks", Communications of the ACM, Feb. 1995; vol. 38, No. 2, pp. 28-29.

Waldspurger et al., "Spawn: A Distributed Computational Economy", IEEE Transactions on Software Engineering, vol. 18, No. 2, Feb. 1992, pp. 103-117 XP002124500.

Yoshida, J., "MPEG-2 Encoders Make Show of Force at NAB", Electronic Engineering Times, Apr. 10, 1995.

Yu, Y. et al., "Software Implementation of MPEG-II Video Encoding Using Socket Programming in LAN", SPIE vol. 2187, pp. 229-240, 1994.

Waltz et al., "Make 'em pay: Billing Net Usage", MacWeek, vol. 6 (No. 27), p. 24 (2) (Dialog full text), (Jul. 27, 1992).

"The Economics of Network Billing: Network Billing and Monitoring Systems can Improve Efficiency and Cut Costs", IBM System User, vol. 14 (No. 11), p. 53 (1) (Dialog Fulltext), (Nov. 1993).

"Let Your Computer Make Money While You Sleep", Newsbytes, p. 1 (Dialog Fulltext), (Aug. 16, 1996).

Regenold et al., "A Single-Chip Multiprocessor DSP Solution for Communication Applications", ASIC Conference and Exhibit 1994, pp. 437-440.

Geppert, L. Solid State [Trend/Development], IEEE Spectrum, v. 33, iss. 1, 1996, pp. 51-55.

Li, Yao, "Free-space Optical Bus-based WDMA Interconnects for Parallel Computation", LEOS '92 Conference Proceedings, Lasers and Electron-Optics Society Annual Meeting, p. 588-589. Nov. 16-19, 1992.

Dickinson et al., "An Integrated Free Space Optical Bus", 1989 IEEE International Conference on Computer Design, VLSI in Computers and Processors, p. 62-65, Oct. 2-4, 1989.

Natarajan et al., "Bi-Directional Optical Backplane Bus for General Purpose Multi-Processor", Journal of Lightwave Technology, vol. 13, No. 6, p. 1031-1040, Jun. 6, 1995.

Zhao et al., "General Purpose Bidirectional Optical Backplane: High Performance Bus for Multiprocessor Systems", Massively Parallel Processing Using Optical Interconnections, 2nd International Conference, p. 188-195, Oct. 23-24, 1995.

Wu et al., "Microprocessor Control Signal Transmission Through Optical Fiber", Conference Record of 1992, IEEE Industry Applications Society Annual Meeting, p. 1747-1750, Oct. 4-9, 1992.

Fox et al, "Towards Web/Java based High Performance Distributed Computing-an Evolving Virtual Machine", www.npac.syr.edu/projects/webspace/doc/hpdc5/paper, Jun. 10, 1996, 11 pages.

None, "PC Vision: Intel unveils plans to bring PCs to Vehicles"; EDGE: Work-Group Computing Report, EDGE Publishing, p. 1-2 (Oct. 28, 1996).

The American Heritage College Dictionary 4th Ed.—definition of "firewall" (2007).

White, "Covert Distributed Processing with Computer Viruses", Advances in Cryptology, Crypto 89, Springer LNCS, v. 435, pp. 616-619 (1990).

Foster et al., "The Grid: Blueprint Infrastructure", Morgan Kaufman for a New Computing Publishers, Inc., 1998.

Hwang et al., "Scalable Parallel Computing", WCB McGraw-Hill, 1998.

Wilkinson, et al., "Parallel Programming", Prentice Hall, 1998.

Patterson et al., "Computer Architecture: A Quantitative Approach" (2nd Edition), Morgan Kaufmann Publishers, Inc., 1996. Culler et al., "Parallel Computer Architecture", Morgan Kaufmann Publishers, Inc., 1998.

Hennessy et al., "Computer Organization and Design", Morgan Kauffmann Publishers, Inc., 1998.

Slater, "The Microprocessor Today", IEEE Micro 1996, pp. 32-44. Steinert-Threlkeld; "New Breed of Chip TI develops a super circuit"; The Sun Baltimore; May 4, 1992.

Dallas Morning News; "LSi holds big plans for tiny chips Versatility of 'system on a chip' creates niche in microelectronics;" Mar. 4, 1996. Mokhoff; "System-on-a-chip comes to wireless arena;" Electronic Engineering Times; Feb. 12, 1996.

Cindi; "System on a Chip' stars at ISSCC;" Electronic News; Feb. 19, 1996.

Ang; "System-on-a-chip to define next-generation set-top box"; Electronic Engineering Times; Dec. 15, 1995.

Marc; "New family microprocessor cores from LSI Logic extends customers' system-on-a-chip design capability" Nov. 7, 1994.

Wall Street Journal; "Technology Brief—Advance Micro Devices Inc.: Company unveils Microship for Hand-Held Computers"; Oct. 18, 1993.

Gelsinger, Patrick et al. "Microprocessors circa 2000," IEEE Spectrum, Oct. 1989 pp. 43-47.

Yu, Albert. "The Future of Microprocessors," IEEE Micro, Dec. 1996, pp. 46-53.

McWilliams. "Dell to Phase Out Computers Using Intel's Itanium," The Wall Street Journal, Online, Sep. 15, 2005.

David Pescovitz, "Power of the PC", Scientific American, pp. 27-28 (Apr. 2000).

Stephen H. Wildstrom, "The Problem with Firewalls", Business Week, pp. 25 (Mar. 20, 2000).

J. Mch., "Build Your Own Supercomputer", FORBES, pp. 228 (Nov. 15, 1999).

Wilkinson, Barry et al., "Parallel Programming: Techniques and Applications Using Networked Workstations and Parallel Computers", Chapter 4, Prentice-Hall, Inc., 1999.

Baker, Lou et. al., "Parallel Programming", Chapter 4, McGraw Hill Companies, Inc., 1996.

Kayssi, A.; Harik, L.; Ferzli, R.; Fawaz, M; "FPGA-based Internet Protocol Firewall Chip"; Electronics, Circuits and Systems, 2000. ICECS 2000. The 7th IEEE International Conference on vol. 1, Dec. 17-20, 2000 pp. 316-319 vol. 1.[retrieved from IEEE database Jun. 9, 2008].

English language abstract of EP 0 647 052, published Apr. 5, 1995. Newton's Telecom Dictionary, "Mobile IP", p. 459, Mar. 1998.

Holographic Quantum Computer, http://www.unitelnw.com/holo1/index (May 1999).

Jonathan Fahey, "Screen Grab", FORBES, pp. 52-53, Mar. 5, 2001. Ronald Grover et al., "TV Guy", Business Week, pp. 66-76, Mar. 12, 2001.

"Distributed Computing", Red Herring, No. 87, pp. 166-202, Dec. 18, 2000

Om Malik, "Distributed Computing Redefines Computer Networks, Underpinning Innovation, Company Formation, and Investments", Red Herring, No. 86, pp. 95-96 and 105, Dec. 4, 2000.

Alan Zeichick, "P2P Network Explained", Red Herring, No. 86, pp. 204 and 206, Dec. 4, 2000.

"Napster is Clouding Grove's Crystal Ball", FORTUNE, pp. 271-272, May 29, 2000.

Gordon Force, Sr., "Portable Data Encryption Approaches", WESTCON/'95, Conference Record: Microelectronics Communications Technology Producing Quality Production Mobile and Portable Power emerging Technologies, Nov. 7-9, 1995, pp. 413-419.

A.D. Romig, Jr., "High Performance Microsystem Packaging: A Perspective", Microelectron Reliab., vol. 37, No. 10/11, pp. 1771-1781 (1997).

File History of U.S. Appl. No. 10/684,657, electronically captured from PAIR on Jul. 19, 2010.

File History of U.S. Appl. No. 08/980,058, electronically captured from PAIR on Jul. 19, 2010.

File History of U.S. Appl. No. 09/085,755, electronically captured from PAIR on Jul. 19, 2010.

File History of U.S. Appl. No. 09/213,875, electronically captured from PAIR on Jul. 19, 2010.

File History of U.S. Appl. No. 09/315,026, electronically captured from PAIR on Jul. 19, 2010.

File History of U.S. Appl. No. 09/315,660, electronically captured from PAIR on Jul. 19, 2010.

File History of U.S. Appl. No. 09/571,558, electronically captured from PAIR on Jul. 19, 2010.

File History of U.S. Appl. No. 09/669,730, electronically captured from PAIR on Jul. 19, 2010.

File History of U.S. Appl. No. 09/884,041, electronically captured from PAIR on Jul. 19, 2010.

File History of U.S. Appl. No. 09/935,779, electronically captured from PAIR on Jul. 19, 2010.

File History of U.S. Appl. No. 10/663,911, electronically captured from PAIR on Jun. 1, 2011.

File History of U.S. Appl. No. 10/802,049, electronically captured from PAIR on Jun. 1, 2011.

File History of U.S. Appl. No. 11/196,527, electronically captured from PAIR on Jun. 1, 2011.

File History of U.S. Appl. No. 11/329,423, electronically captured from PAIR on Oct. 11,2012.

File History of U.S. Appl. No. 11/338,887, electronically captured from PAIR on Jun. 1, 2011.

File History of U.S. Appl. No. 12/164,661, electronically captured from PAIR on Oct. 11, 2012.

File History of U.S. Appl. No. 12/364,745, electronically captured from PAIR on Oct. 11, 2012.

File History of U.S. Appl. No. 12/499,555, electronically captured from PAIR on Oct. 11, 2012.

File History of U.S. Appl. No. 12/822,928, electronically captured from PAIR on Oct. 11, 2012.

File History of U.S. Appl. No. 12/829,120, electronically captured from PAIR on Oct. 11, 2012.

File History of U.S. Appl. No. 13/016,149, electronically captured from PAIR on Oct. 11, 2012.

File History of U.S. Appl. No. 13/018,089, electronically captured from PAIR on Oct. 11, 2012.

O. M. Woodward et al., "The Omniguide Antenna; An Omnidirectional Waveguide Array for UHF-TV Broadcasts", IRE International Convention Records, pp. 37-39, Mar. 1955.

File History of U.S. Appl. No. 13/180,164, electronically captured from PAIR on Oct. 11, 2012.

File History of U.S. Appl. No. 13/240,842, electronically captured from PAIR on Oct. 11, 2012.

File History of U.S. Appl. No. 13/283,274, electronically captured from PAIR on Oct. 11, 2012.

File History of U.S. Appl. No. 13/495,867, electronically captured from PAIR on Oct. 11, 2012.

File History of U.S. Appl. No. 13/599,484, electronically captured from PAIR on Oct. 11, 2012.

Hare et al., "Master the Complexities of Network Security", Internet Firewalls and Network Security, Second Edition, pp. 325-350 and 516, Aug. 1996.

File History of U.S. Appl. No. 13/016,149.

File History of U.S. Appl. No. 13/018,089.

File History of U.S. Appl. No. 12/829,120.

File History of U.S. Appl. No. 13/180,164. File History of U.S. Appl. No. 13/495,867. File History of U.S. Appl. No. 13/599,484.

\* cited by examiner

Primary Examiner — Mohammad W Reza (74) Attorney, Agent, or Firm — DLA Piper LLP US

#### (57) ABSTRACT

A microchip for a computer configured to connect to at least one network of computers. The microchip includes at least a first internal hardware firewall configured to deny access to at least a first protected portion of said microchip from said network, and at least one general purpose microprocessor including at least two general purpose core or general purpose processing units. At least a first core or processing unit is located within the first protected portion of the microchip. At least a second core or processing unit is located within a second portion of the microchip that is not protected by at least said first internal hardware firewall. At least the second core or processing unit is separated from the first core or processing unit by at least the first internal hardware firewall and is located between at least the first internal hardware firewall and the at least one network.

#### 20 Claims, 35 Drawing Sheets

FIG. 10M

FIG. 10Q

FIG. 11

FIG. 13

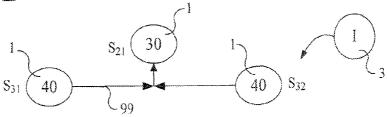

FIG. 16A

FIG. 16B

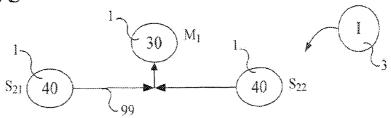

FIG. 16C

FIG. 16D

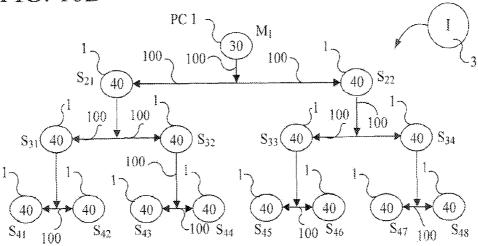

FIG. 16E

FIG. 16L

FIG. 16M

FIG. 16N

FIG. 16T

FIG. 16X

FIG. 16Y

FIG. 16AA

FIG. 16AB

FIG. 17C

FIG. 18A

FIG. 18B

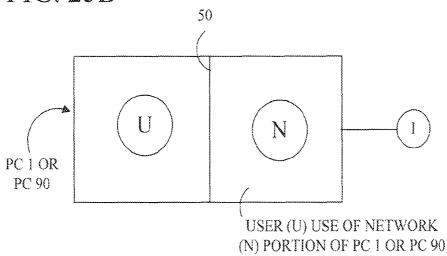

FIG. 20B

FIG. 21A

FIG. 21B

FIG. 22B

FIG. 22C

PC 1

PC 1 OR

PC 90

99 OR

100

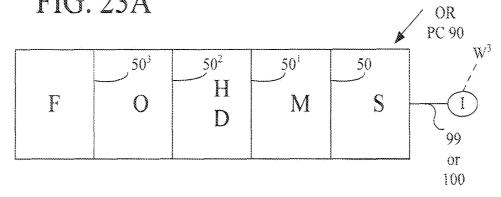

FIG. 23A

FIG. 23B

FIG. 23D FIG. 23E  $A^{1}$  $O^1$ 50<sup>A¹</sup> 50<sup>O1</sup> 50<sup>A<sup>2</sup></sup>  $50^{\text{A}^3}$   $50^{\text{A}^4}$ 50<sup>O²</sup>  $50^{0^3}$   $50^{0^4}$

FIG. 24 61, HD CONTROLLER 50  $\mathbf{O}^{r^1}$  $r_{o}$  $W_0$ 99 OR 100 **OPTIONAL** HD ΗĎ R R/W HEAD **HEAD** (OPTIONAL W) **LOWER** <u>UPPER</u> HD 61 SURFACE OF SURFACE OF **PLATTER PLATTER**

FIG. 25A

FIG. 25B

NÈTWORK (N) USE OF NETWORK (N) PORTION OF PC 1 OR PC 90

FIG. 25D

PC 90

Microchip (or PCI)

200

202 (or 203)

**Bottom View**

Fig. 28

Oct. 8, 2013

Fig. 29B

Oct. 8, 2013

Fig. 30C 502<sup>3</sup> or 502<sup>2</sup>

Fig. 31

# MICROCHIPS WITH AN INTERNAL HARDWARE FIREWALL

#### CROSS REFERENCE TO RELATED APPLICATIONS

This application is a Continuation of U.S. patent application Ser. No. 12/164,661, filed Jun. 30, 2008, which is a Divisional of U.S. patent application Ser. No. 10/684,657, filed Oct. 15, 2003 (now abandoned), which, in turn, claims 10 the benefit of U.S. Provisional Application No. 60/418,177, filed Oct. 15, 2002. U.S. patent application Ser. No. 10/684, 657 is also Continuation-in-Part of International Application No. PCT/US02/29227, filed Sep. 16, 2002, which claims the benefit of U.S. Provisional Application Nos. 60/322,474, 15 filed Sep. 17, 2001, and 60/323,701, filed Sep. 21, 2001. U.S. patent application Ser. No. 10/684,657 is also a Continuationin-Part of U.S. patent application Ser. No. 09/935,779, filed Aug. 24, 2001 (now U.S. Pat. No. 7,506,020), which claims the benefit of U.S. Provisional Application Nos. 60/308,826, 20 filed Aug. 1, 2001, and 60/227,660, filed Aug. 25, 2000. U.S. patent application Ser. No. 09/935,779 is also a Continuationin-Part of U.S. patent application Ser. No. 09/571,558, filed May 16, 2000 (now U.S. Pat. No. 7,035,906), which claims the benefit of U.S. Provisional Application Nos. 60/135,851, 25 filed May 24, 1999, 60/136,759, filed May 28, 1999, and 60/135,852, filed May 24, 1999. U.S. patent application Ser. No. 09/935,779 is also a Continuation-in-Part of U.S. patent application Ser. No. 09/315,026, filed May 20, 1999 (now U.S. Pat. No. 7,024,449), which claims the benefit of U.S. 30 Provisional Application Nos. 60/134,552, filed May 17, 1999, 60/086,516, filed May 22, 1998, 60/086,588 filed May 22, 1998, 60/086,948, filed May 27, 1998, 60/087,587, filed Jun. 1, 1998, and 60/088,459, filed Jun. 8, 1998. U.S. patent Part of U.S. patent application Ser. No. 09/213,875, filed Dec. 17, 1998 (now U.S. Pat. No. 6,725,250), which claims the benefit of U.S. Provisional Application Nos. 60/068,366, filed Dec. 19, 1997, 60/086,516, filed May 22, 1998, 60/086, 588 filed May 22, 1998, 60/086,948, filed May 27, 1998, 40 60/087,587, filed Jun. 1, 1998, and 60/088,459, filed Jun. 8, 1998, and which is a Continuation-in-Part of U.S. patent application Ser. No. 08/980,058, filed Nov. 26, 1997 (now U.S. Pat. No. 6,732,141), which, in turn, claims the benefit of U.S. Provisional Application Nos. 60/066,415, filed Nov. 24, 45 1997, 60/066,313, filed Nov. 21, 1997, 60/033,871, filed Dec. 20, 1996, 60/032,207 filed Dec. 2, 1996, and 60/031,855, filed Nov. 29, 1996. U.S. patent application Ser. No. 09/935, 779 is also a Continuation-in-Part of U.S. patent application Ser. No. 09/085,755, filed May 27, 1998 (now U.S. Pat. No. 50 7,634,529), which claims the benefit of U.S. Provisional Application Nos. 60/066,313, filed Nov. 21, 1997, 60/066, 415, filed Nov. 24, 1997, 60/068,366, filed Dec. 19, 1997, 60/086,516, filed May 22, 1998, and 60/086,588, filed May 22, 1998. U.S. patent application Ser. No. 09/571,558 is also 55 a Continuation-in-Part of U.S. patent application Ser. Nos. 09/315,026, 09/085,755, and 09/213,875, whose respective priorities are discussed above. U.S. patent application Ser. No. 09/315,026 is also a Continuation-in-Part of International Application No. PCT/US98/27058, filed Dec. 17, 1998, 60 which claims the benefit of U.S. Provisional Application No. 60/068,366, filed Dec. 19, 1997. U.S. patent application Ser. No. 09/315,026 is also a continuation-in part of PCT application PCT/US97/21812, filed Nov. 28, 1997, which claims the benefit of U.S. Provisional Application Nos. 60/033,871, 65 filed Dec. 20, 1996, 60/032,207, filed Dec. 2, 1996, and 60/031,855, filed Nov. 29, 1996. U.S. patent application Ser.

2

No. 09/085,755 is also a continuation-in-part of U.S. patent application Ser. No. 08/980,058 and PCT application PCT/ US97/21812, whose respective priorities are discussed above. U.S. patent application Ser. No. 09/315,026 is also a continuation-in-part of U.S. patent application Ser. Nos. 09/085,755 and 09/213,875, whose respective priority is discussed above. The contents of all the above applications are incorporated herein in their entirety by reference.

#### BACKGROUND OF THE INVENTION

This invention relates generally to one or more computer networks that include computers, such as personal computers (PC's) or network computers such as servers, which have microprocessors linked by broadband transmission means and have hardware, software, firmware, and other means such that at least two parallel processing operations occur that involve at least two sets of computers in the network or in interconnected networks. This invention constitutes a form of

More particularly, this invention relates to one or more large networks, like the Internet, which comprise smaller networks and large numbers of interconnected computers, wherein multiple separate parallel or massively parallel processing operations involving multiple different sets of computers occur simultaneously. Even more particularly, this invention relates to one or more such networks wherein multiple parallel or massively parallel microprocessing processing operations occur separately or in an interrelated fashion, and wherein ongoing network processing linkages are established between virtually any microprocessors of separate computers connected to the network.

Still more particularly, this invention relates generally to a application Ser. No. 09/935,779 is also a Continuation-in- 35 network structure or architecture that enables the shared use of network microprocessors for parallel processing, including massive parallel processing, and other shared processing such as multitasking, wherein personal computer owners provide microprocessor processing power to a network, such as for parallel or massively parallel processing or multitasking, in exchange for network linkage to other personal computers and other computers supplied by network providers such as Internet Service Providers (ISP's), including linkage to other microprocessors for parallel or other processing such as multitasking. The financial basis of the shared use between owners and providers may be whatever terms to which the parties agree, subject to governing laws, regulations, or rules, including payment from either party to the other based on periodic measurement of net use or provision of processing power like a deregulated electrical power grid or involving no payment. The network system may provide an essentially equivalent usage of computing resources by both users and providers since any network computer operated by either entity is potentially both a user and provider of computing resources alternately or simultaneously, assuming multitasking is operative. A user may have an override option exercised on the basis of, for example, a user profile, a user's credit line, or relatively instant payment.

This invention also relates to a network system architecture including hardware and software that provides use of the Internet or other network, without cost, to users of personal computers or other computers, while also providing users with computer processing performance that at least doubles every 18 months through metacomputing means. This metacomputing performance increase provided by the new Grid (or MetaInternet) is in addition to other performance increases, such as those already anticipated by Moore's Law.

The computer industry has been governed over the last 30 years by Moore's Law, which holds that the circuitry of computer chips shrinks substantially each year, yielding a new generation of chips every 18 months with twice as many transistors, such that microprocessor computing power effec- 5 tively doubles every year-and-a-half.

The long-term trend in computer chip miniaturization is projected to continue unabated over the next few decades. For example, slightly more than a decade ago a 16 kilobit DRAM (dynamic random access memory) memory chip (storing 16,000 data bits) was typical; the standard in 1996 was the 16 megabit chip (16,000,000 data bits), which was introduced in 1993; industry projections are for 16 gigabit memory chips (16,000,000,000 data bits) to be introduced in 2008 and 64 gigabit chips in 2011; and 16 terabit chips (16,000,000,000, 000 data bits) may be conceivable by the mid-to-late 2020's, by which time such microchips may have become nanochips in terms of their circuit dimensions. This is a thousand-fold increase regularly every fifteen years. Hard drive speed and 20 capacity are also growing at a spectacular rate, even higher in recent years than that of semiconductor microchips.

Similarly, regular and enormous improvements may continue in microprocessor computing speeds, whether measured in simple clock speed or MIPS (millions of instructions 25 per second) or numbers of transistors per chip. For example, performance has improved by four or five times every three years since Intel launched its X86 family of microprocessors used in the currently dominant "Wintel" standard personal computers. The initial Intel Pentium Pro microprocessor was introduced in 1995 and is a thousand times faster than the first IBM standard PC microprocessor, the Intel 8088, which was introduced in 1979. By 1996 the fastest of microprocessors, even the microprocessor of the Nintendo 64 video game system, were faster than the processor in the original Cray Y-MP supercomputer.

Microprocessors, software, firmware, and other components are also evolving from 8-bit and 16-bit systems into the 40 32-bit systems that are becoming the standard today, with some 64-bit systems like the DEC Alpha already introduced and more coming, such as Intel's Itanium microprocessor in 2001, with future increases to 128-bit systems likely.

A second major development trend in the past decade or so 45 has been the rise of parallel processing, a computer architecture utilizing more than one CPU microprocessor linked together into a single computer with new operating systems having modifications that allow such an approach. Thousands of relatively simple microprocessors may be used together for 50 massively parallel processing. The field of supercomputing has been overtaken by this approach, which includes designs utilizing many identical standard personal computer microprocessors.

Hardware, firmware, software, and other components spe- 55 cific to parallel processing are in a relatively early stage of development compared to that for single processor computing. Therefore, much further design and development are expected in the future to better maximize the computing capacity made possible by parallel processing. Continued 60 improvement is anticipated in system hardware, software, and architectures for parallel processing so that reliance on the need for multiple microprocessors to share a common central memory is reduced, thereby allowing more independent operation of those general purpose microprocessors, 65 each with their own discrete memory, like current personal computers, workstations, and most other computer systems

architecture. For unconstrained operation, each individual microprocessor should have rapid access to sufficient memory.

Several models of personal computers having more than one general purpose microprocessor are now available. In the future, personal computers, broadly defined to include versions not currently in use, will likely also employ parallel computing utilizing multiple microprocessors or massively parallel computing with very large numbers of microprocessors. Future designs, such as Intel's Itanium chip, are expected to have a significant number of parallel processors on a single microprocessor chip.

A form of parallel processing called superscalar processing is also being employed within microprocessor design. The current generation of microprocessors, such as the Intel Pentium, have more than one data path within the microprocessor in which data is processed, with two to three paths being typical now and as many as eight in 1998 in IBM's new Power 3 microprocessor chip.

A third major development trend is the increasing size of bandwidth, which is a measure of communications power or transmission speed, in terms of units of data per second, between computers connected by a network. Previously, the local area networks and telephone lines typically linking computers including personal computers have operated at speeds much lower than the processing speeds of a personal computer. For example, a typical 1997 Intel Pentium operates at 100 MIPS, whereas the most common current Ethernet connecting PC's is roughly 10 times slower at 10 megabits per second (Mbps), although some Ethernet connections are now 100 Mbps and telephone lines are very much slower, the highest typical speed in 1998 being the approximately 56 kilobits reached during downloads.

The situation is expected to change dramatically. Bandsuch as Digital Equipment Corporation's Alpha chip, and 35 width or transmission speed is anticipated to expand from 5 to 100 times as fast as the rise of microprocessor speeds, due to the use of coaxial cable, wireless, and especially fiber optic cable and optical wireless, instead of old telephone twisted pair lines, and due to the use of wideband communication such as dense wave division multiplexing (DWDM) and wideband code division multiple access (CDMA), as well as ultrawideband wireless. In DWDM systems, multiple channels are transmitted over a single fiber because they are sent at different wavelengths. Telecommunication providers are now making available single fiber connections supporting a bandwidth of 40 gigabits per single fiber, and, alternatively, as many as 160 wavelength channels (lambdas) per single fiber. In CDMA systems, users are multiplexed across the same spectrum, with each user being assigned a different instance of a noise-like carrier wave.

> Technical improvements are expected in the near term which will make it possible to carry over 2 gigahertz (billions of cycles per second) on each of 700 wavelength channels (lambdas), adding up to more than 1,400 gigahertz on a single fiber thread. Experts have estimated that the bandwidth of optical fiber has been utilized one million times less fully than the bandwidth of coaxial or twisted pair copper lines. Within a decade, 10,000 wavelength streams per fiber are expected; 20 to 80 wavelengths on a single fiber is already commercially available. The use of thin mirrored hollow wires or tubes called omniguides may also provide very substantial additional increases.

> Other network connection developments, such as asynchronous transfer mode (ATM) and digital signal processors, whose price/performance ratio has improved tenfold every two years, are also supporting the rapid increase in bandwidth. The increase in bandwidth reduces the need for switch-

ing, and switching speed will be greatly enhanced when practical optical switches are introduced in the near future, potentially reducing costs substantially.

The result of this huge bandwidth increase is extraordinary: already it is technically possible to connect virtually any computer to a network with a bandwidth that equals or exceeds the computer's own internal system bus speed, even as that bus speed itself is increasing significantly. The principal constraint is the infrastructure, consisting mostly of connecting the "last mile" to personal computers with optical 10 fiber or other broad bandwidth connections, which still need to be built. The system bus of a computer is its internal network connecting many or most of its internal components such as microprocessor, random access memory (RAM), hard drive, modem, floppy drive, and CD-ROM; for recent per- 15 sonal computers, the system bus has been only about 40 megabits per second, but is up to 133 megabits per second on Intel's Pentium PCI bus in 1995. IBM's 1998 Power 3 microprocessor chip has a system bus of 1.6 gigabits per second and there is now up to a gigabit per second on Intel's Pentium PCI 20

Despite these tremendous improvements anticipated in the future, a typical PC is already so fast that its microprocessor is essentially idle during most of the time the PC is in actual use, and the operating time itself is but a small fraction of 25 those days the PC is even in use at all. Nearly all PC's are essentially idle during roughly all of their useful life. A microprocessor of a PC may be in an idle state 99.9% of the time, disregarding unnecessary microprocessor busywork such as executing screen saver programs, which have been made 30 essentially obsolete by power-saving CRT monitor technology, which is now standard in the PC industry.

Because the reliability of PC's is so exceptionally high now, with the mean time to failure of all components typically several hundred thousand hours or more, the huge idle time of 35 PC's represents a total loss; given the high capital and operating costs of PC's, the economic loss is very high. PC idle time does not in effect store a PC, saving it for future use, since the principle limiting factor to continued use of today's PC's is obsolescence, not equipment failure resulting from 40 use

Moreover, there is continuing concern that Moore's Law, which holds that the constant miniaturization of circuits results in a doubling of computing power every 18 months, cannot continue to hold true much longer. Indeed, Moore's 45 Law may now be nearing its limits for silicon-based devices, perhaps by as early as 2010. No new technologies have yet emerged that seem to have the potential for development to a practical level by then, although many recent advances have the potential to maintain Moore's Law.

### SUMMARY OF THE INVENTION

However, the confluence of all three of the established major trends summarized above—supercomputer-like personal computers, the spread of parallel processing using personal computer general purpose microprocessors (particularly massively parallel processing), and the enormous increase in network communications bandwidth—enables a solution to the excessive idleness problem of personal computers and the possible end of Moore's Law. The solution may achieve very high potential economic savings once the basic infrastructure connecting personal computers with optical fiber is in place in the relatively near future.

The solution is to use those mostly idle PC's (or their 65 equivalents or successors) to build a parallel or massively parallel processing computer or computers utilizing a very

6

large network, like the Internet or, more specifically, like the World Wide Web (WWW), or their equivalents or eventual successors like the Grid or MetaInternet (and including Internet II and the Next Generation Internet, which are under development now and which will utilize much broader bandwidth and will coexist with the Internet, the structure of which is in ever constant hardware and software upgrade and including the Superinternet based on essentially all optical fiber transmission) with extremely broad bandwidth connections and virtually unlimited data transmission speed.

A prime characteristic of the Internet is the very large number of computers of all sorts already linked thereto, with the future potential for an effectively universal connection. The Internet is a network of networks of computers that provides nearly unrestricted access worldwide. The currently existing and soon-to-be widely available very broad bandwidth of network communications is used to link personal computers externally in a manner at least equivalent to, and probably much faster than, the faster internal system buses of the personal computers, so that no external processing constraint is imposed on linked personal computers by data input, output, or throughput; the speed of the microprocessor itself and the internal connections or buses of the PC are the only processing constraint of the system.

This makes possible efficient external parallel processing (and multitasking), including massively parallel processing, in a manner paralleling more conventional internal parallel processing, called superscalar processing.

In one embodiment, the World Wide Web is transformed into a huge virtual massively parallel processing computer or computers, with potential through its established hyperlinks connections to operate in a manner at least somewhat like a neural network or neural networks, since the speed of transmission in the broadband linkages is so great that any linkage between two microprocessors is virtually equivalent to direct, physically close connections between those microprocessors.

With further development, digital signal processor-type microprocessors and/or analogue microprocessors may be particularly advantageous for this approach, either alone or in conjunction with conventional microprocessors and/or the new microprocessors described below. Networks with WWW-type hyperlinks incorporating digital signal processor-type microprocessors could operate separately from networks of conventional microprocessors or with one or more connections between such differing networks or with relatively complete integration between such differing networks. Simultaneous operation across the same network connection structure should be possible, employing non-interfering transmission links.

Such extremely broad bandwidth networks of computers enable every PC within the network to be fully utilized or nearly so. Because of the extraordinary extent to which existing PC's are currently idle, at optimal performance this new system may result in a thousand-fold increase in computer power available to each and every PC user, and, on demand, almost any desired level of increased power, limited mostly by increased cost, which however are relatively far less than possible from other conceivable computer network configurations. This revolutionary increase is in addition to the extremely rapid, but evolutionary increases already occurring in the computer/network industry, as discussed above.

The metacomputing hardware and software means of the Grid (or MetaInternet) provides performance increases that are likely to at least double every eighteen months based on the doubling of personal computers shared in a typical parallel processing operation by a standard PC user, starting first with at least 2 PC's, then about 4, about 8, about 16, about 32,

about 64, about 128, about 256, and about 512, for example. After about fifteen years, for example, it is anticipated that each standard PC user will likely be able to use a maximum of about 1,024 personal computers for parallel processing or any other shared computing use, while generally using for free the 5 Internet or its successors, like the Grid (or MetaInternet). At the other end of the performance spectrum, supercomputers experience a similar performance increase generally, but ultimately the performance increase is limited primarily by the cost of adding network linkages to available PC's, so there is 10 definite potential for a huge leap in supercomputer perfor-

Network computer systems as described above offer almost limitless flexibility due to the abundant supply of heretofore idle connected microprocessors. This advantage 15 allows "tightly coupled" computing problems, which normally are difficult to process in parallel, to be solved without knowing in advance how many processors are available (as is now necessary in relatively massively parallel processing), what they are, and their connection characteristics. A mini- 20 mum number of equivalent processors (with equivalent other specifications) are easily found nearby in a massive network like the Internet and assigned within the network from those multitudes available nearby. Moreover, the number of microthe complexity of the problem, and limited only by cost. The existing problem of time delay is solved largely by the widespread introduction of broad bandwidth connections between computers processing in parallel.

The state of the known art relating to this application is 30 summarized in The Grid: Blueprint for a New Computing Infrastructure, edited by Ian Foster and Carl Kesselman, and published by Morgan Kaufman Publishers, Inc. in 1998. The state of the known art relating to this application is also summarized in: Scalable Parallel Computing by Kai Hwang 35 and Zhiwei Xu, published by WCB McGraw-Hill in 1998; Parallel Programming by Barry Wilkinson and Michael Allen, published by Prentice Hall in 1998; Computer Architecture: A Quantitative Approach (2nd Edition) by David Patterson and John Hennessy, published by Morgan Kauf- 40 mann in 1996; Parallel Computer Architecture by David Culler and Jaswinder Singh, published by Morgan Kaufman in 1998; and Computer Organization and Design by John. Hennessy and David Patterson, published by Morgan Kaufman in 1998.

# BRIEF DESCRIPTION OF THE DRAWINGS

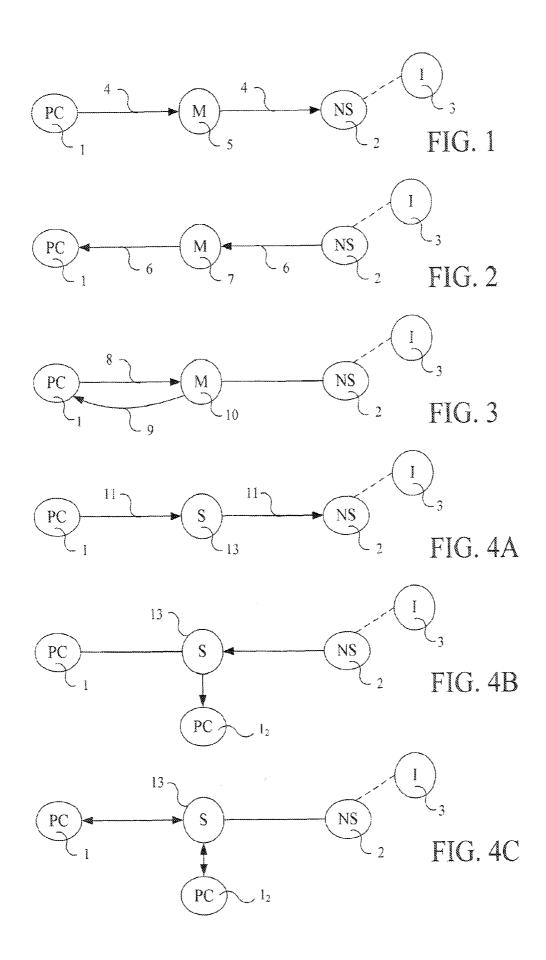

FIG. 1 is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of a 50 meter means which measures flow of computing during a shared operation such as parallel processing between a typical PC user and a network provider.

FIG. 2 is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of 55 another meter means which measures the flow of network resources, including shared processing, being provided to a typical PC user and a network provider.

FIG. 3 is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of 60 another meter means which, prior to execution, estimates the level of network resources, and their cost, of a shared processing operation requested by a typical PC user from a network provider.

FIGS. 4A-4C are simplified diagrams of a section of a 65 computer network, such as the Internet, showing in a sequence of steps an embodiment of a selection means

whereby a shared processing request by a PC is matched with a standard preset number of other PC's to execute a shared operation.

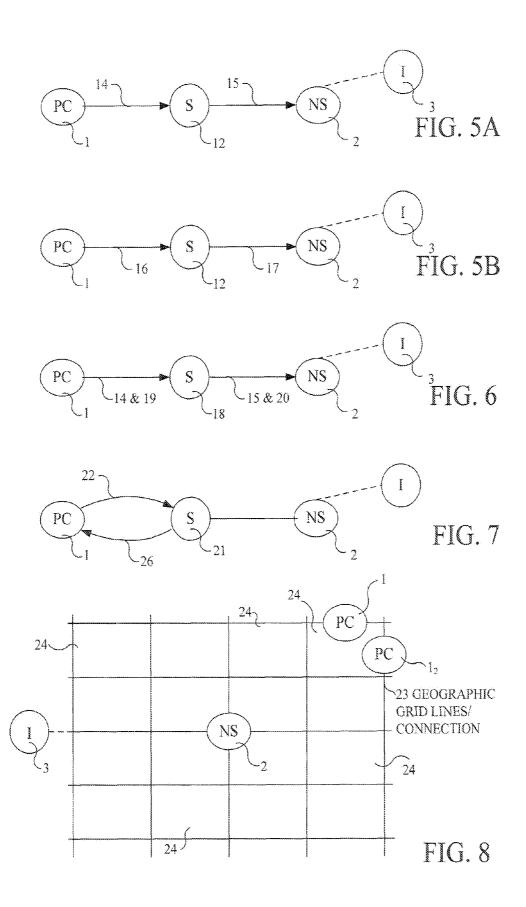

FIGS. 5A and 5B are simplified diagrams of a section of a computer network, such as the Internet, showing embodiments of a control means whereby the PC, when idled by its user, is made available to the network for shared processing

FIG. 6 is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of a signal means whereby the PC, when idled by its user, signals its availability to the network for shared processing opera-

FIG. 7 is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of a receiver and/or interrogator means whereby the network receives and/or queries the availability for shared processing status of a PC within the network.

FIG. 8 is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of a selection and/or utilization means whereby the network locates available PC's in the network that are located closest to each other for shared processing.

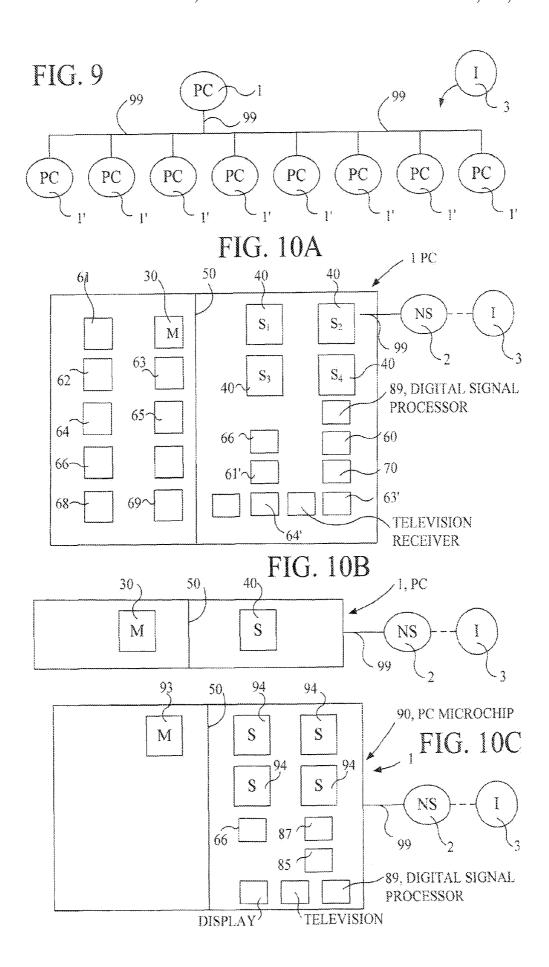

FIG. 9 is a simplified diagram of a section of a computer processors used are almost completely flexible, depending on 25 network, such as the Internet, showing an embodiment of a system architecture for conducting a request imitated by a PC for a search using parallel processing means that utilizes a number of networked PC's.

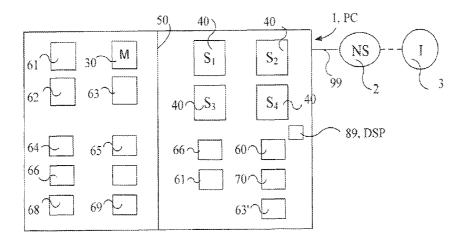

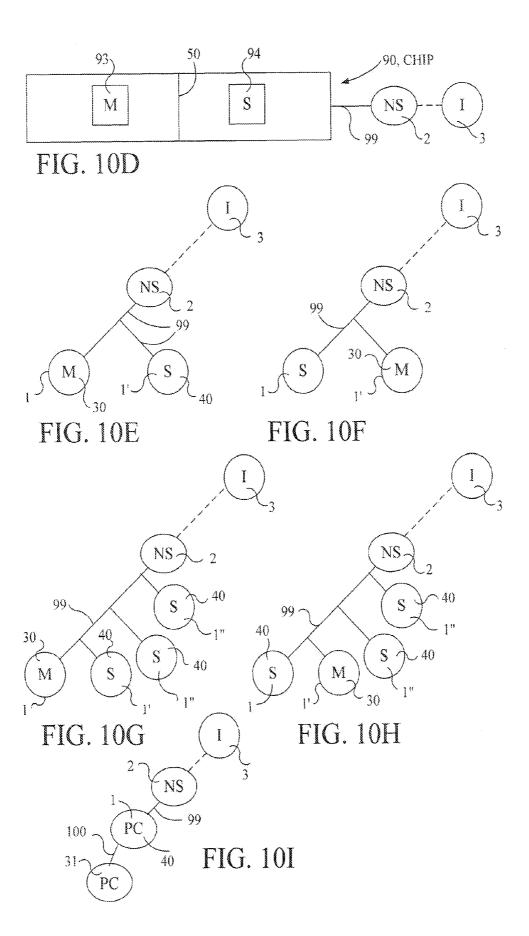

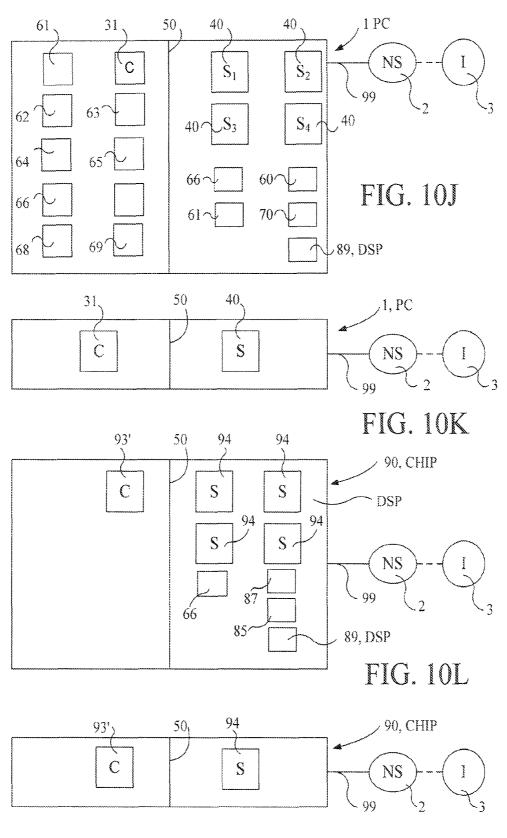

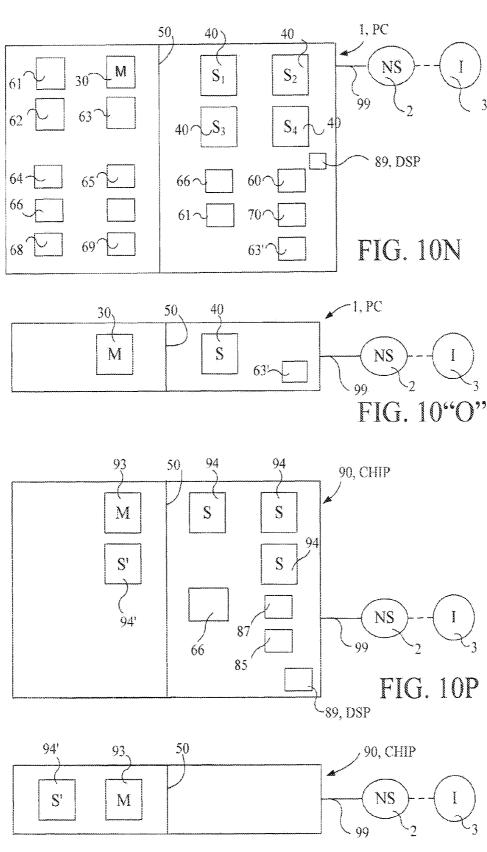

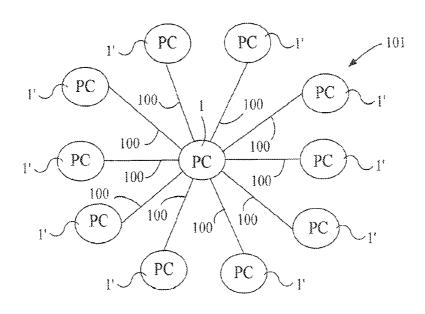

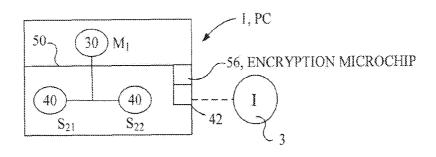

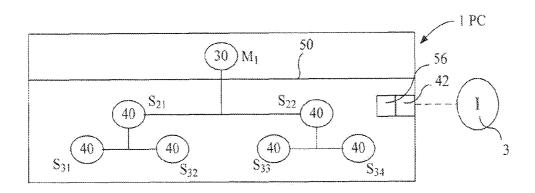

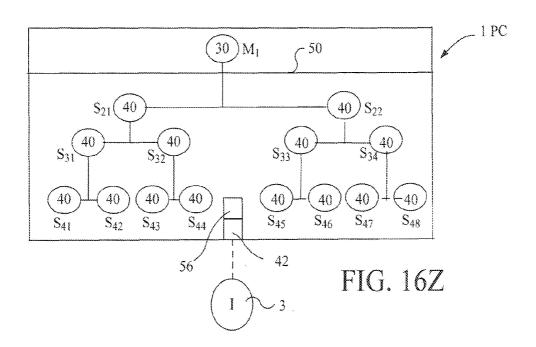

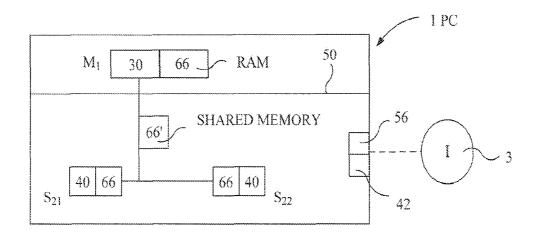

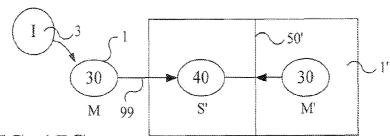

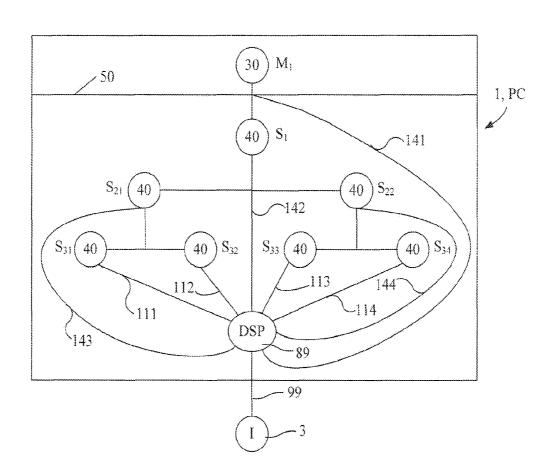

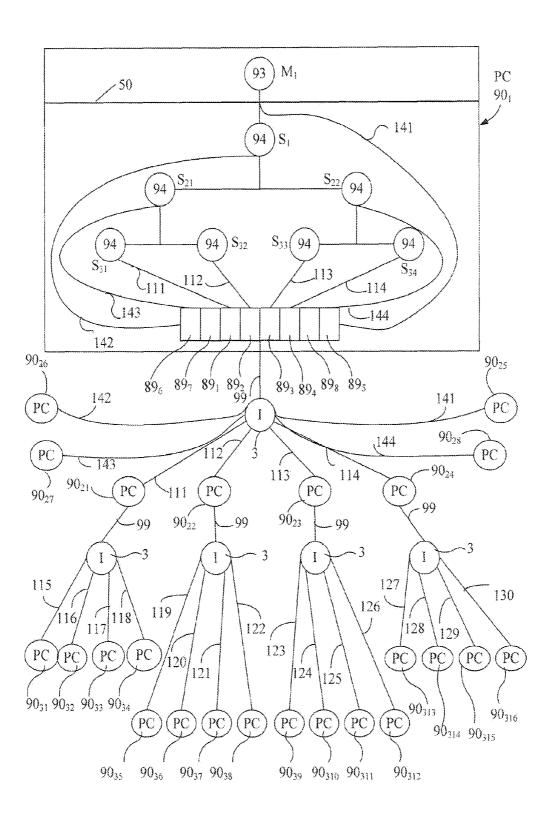

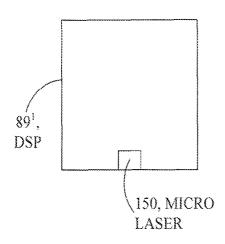

> FIGS. 10A-10Q are simplified diagrams of a section of a computer network, such as the Internet, showing an embodiment of a system architecture utilizing a firewall to separate that part of a networked PC (including a system reduced in size to a microchip) that is accessible to the network for shared processing from a part that is kept accessible only to the PC user; also sowing the alternating, role that preferably each PC in the network can play as either a master or slave in a shared processing operation involving one or more slave PC's in the network; showing a home or business network system; in addition, showing PC and PC microchips controlled by a controller (including remote) with limited or no processing capability; and showing PC and PC microchips in which a firewall **50** is can be reconfigured by a PC user.

FIG. 11 is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of a 45 system architecture for connecting clusters of PCs to each other by wireless means, to create the closest possible (and therefore fastest) connections.

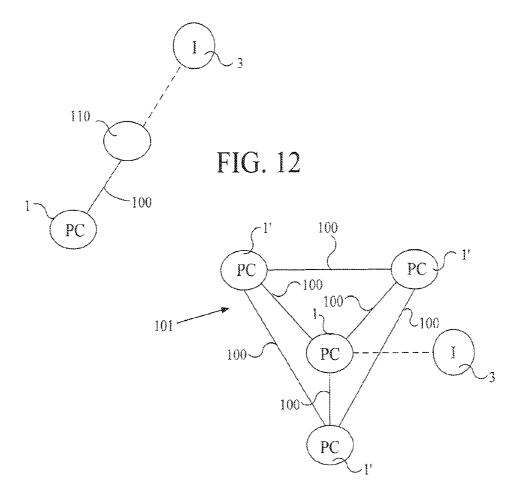

FIG. 12 is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of a system architecture for connecting PC's to a satellite by wire-

FIG. 13 is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of a system architecture providing a cluster of networked PC's with complete interconnectivity by wireless means.

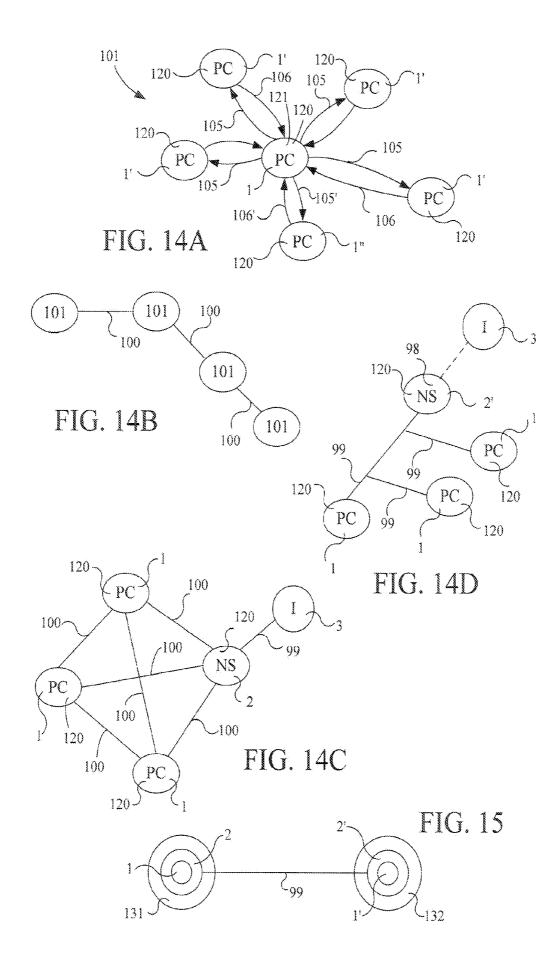

FIG. 14A is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of a transponder means whereby a PC can identify one or more of the closest available PC's in a network cluster to designate for shared processing by wireless means. FIG. 14B shows clusters connected wirelessly. FIG. 14C shows a wireless cluster with transponders and with a network wired connection to the Internet. FIG. 14D shows a network client/server wired system with transponders.

FIG. 15 is a simplified diagram of a section of a computer network, such as the Internet, showing an embodiment of a routing means whereby a PC request for shared processing is

routed within a network using broad bandwidth connection means to another area in a network with one or more idle PC's available.

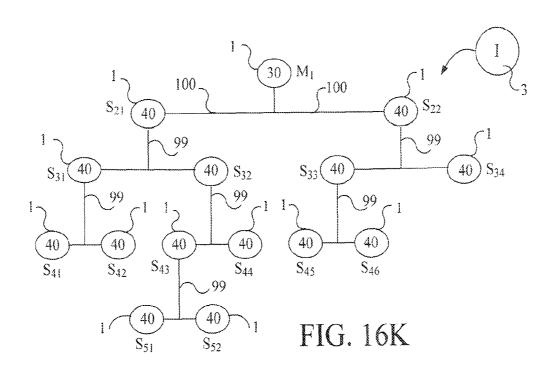

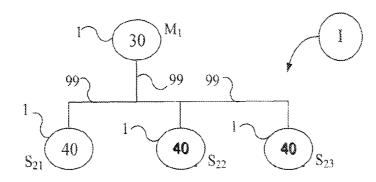

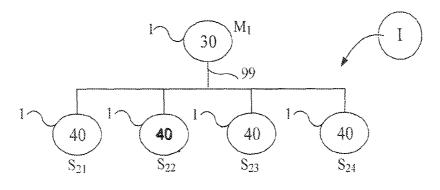

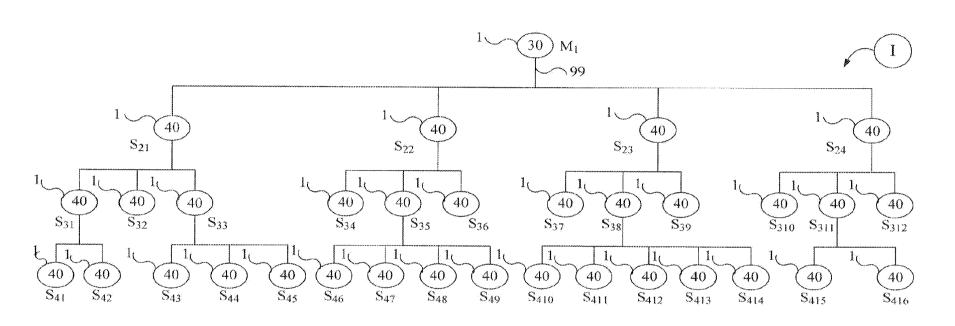

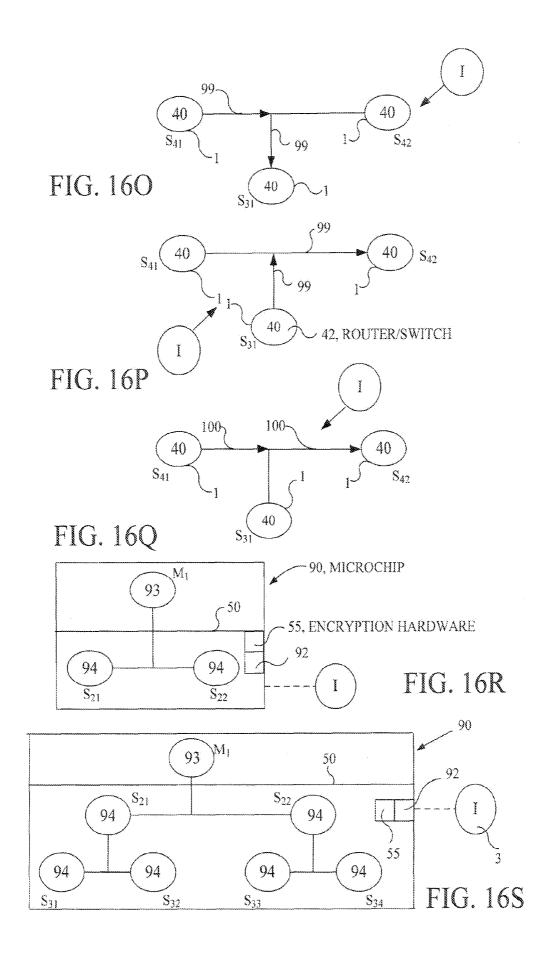

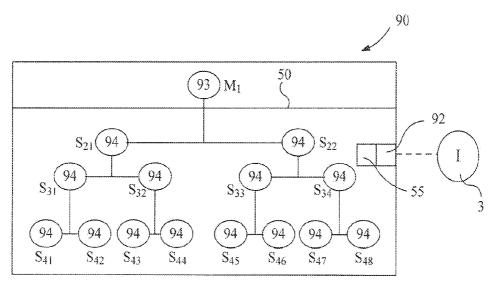

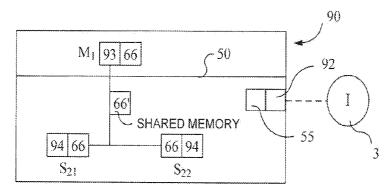

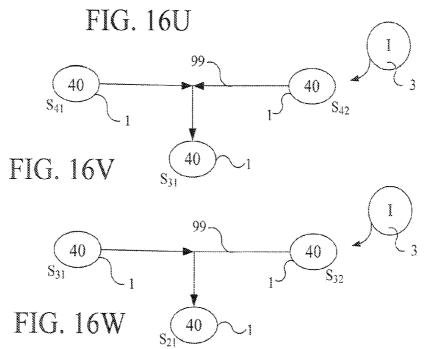

FIGS. 16A-16Z, 16AA, and 16AB show a new hierarchical network architecture for personal computers and/or micro- 5 processors based on subdivision of parallel processing or multi-tasking operations through a number of levels down to a processing level.

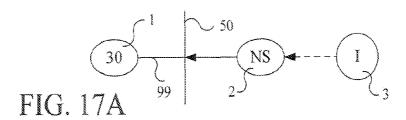

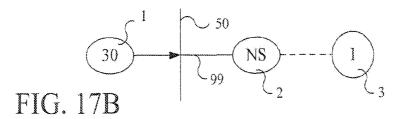

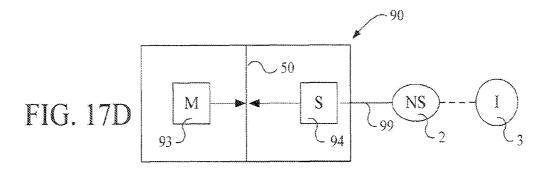

FIGS. 17A-17D show an internal firewall 50 with a dual function, including that of protecting Internet users (and/or 10 other network users sharing use) of one or more slave personal computers PC 1 or microprocessors 40 from unauthorized surveillance or intervention by an owner/operator of those slave processors.

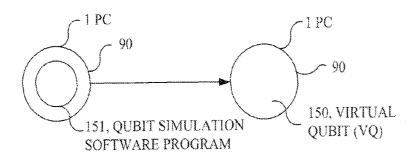

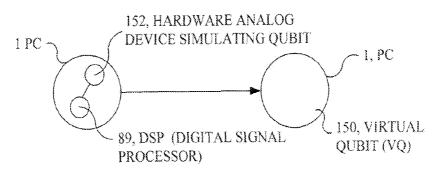

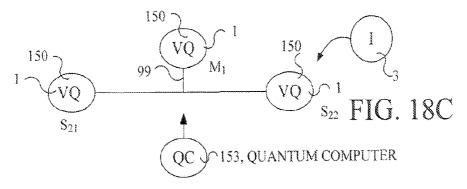

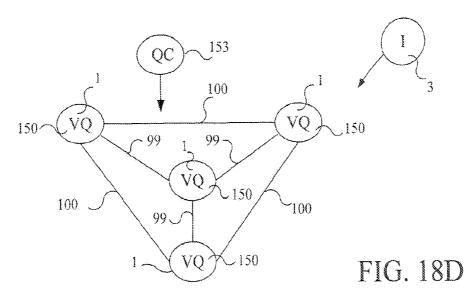

FIGS. 18A-18D show designs for one or more virtual 15 quantum computers integrated into one or more digital computers.

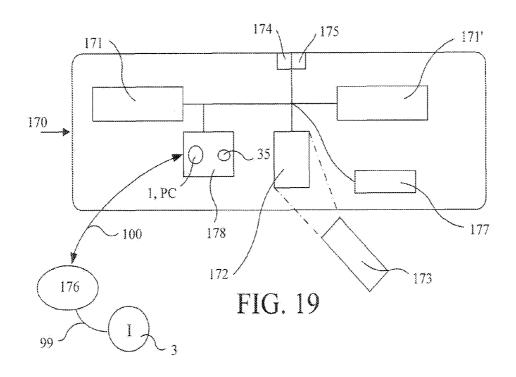

FIG. 19 shows special adaptations to allow the use of idle automobile computers to be powered and connected to the Internet (or other net) for parallel or multi-tasking processing. 20

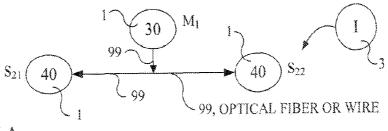

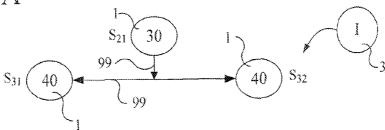

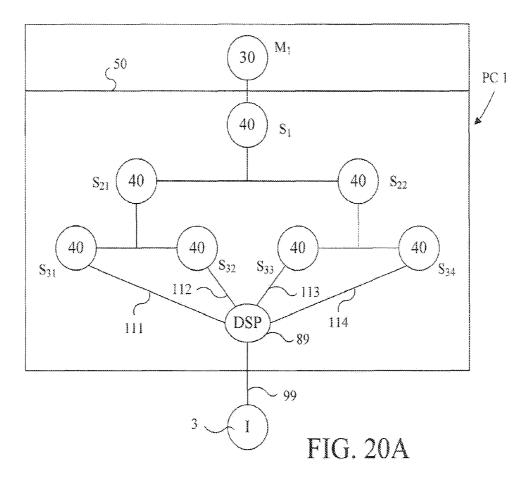

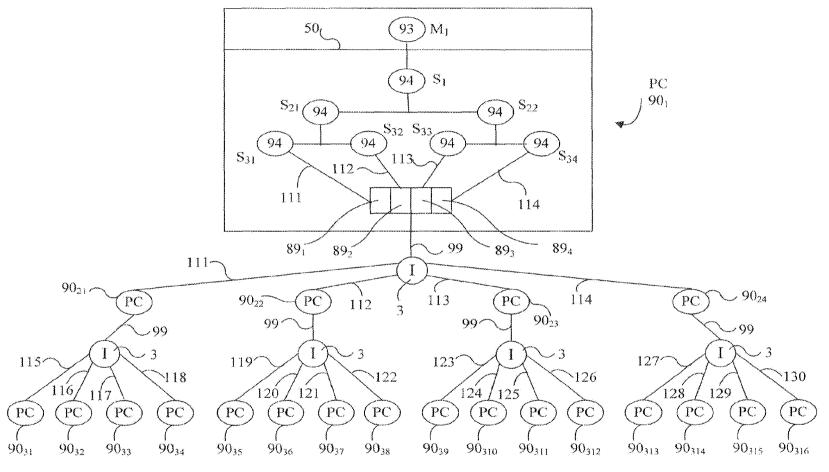

FIGS. 20A and 20B show separate broad bandwidth outputs or inputs such as an optical connection like glass fiber from each microprocessor 40 or 94.

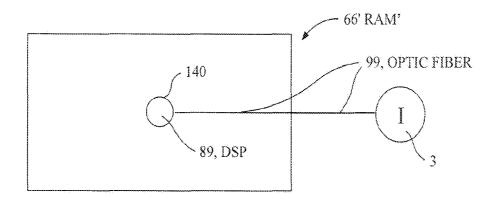

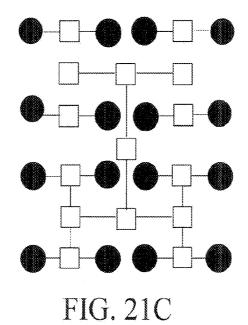

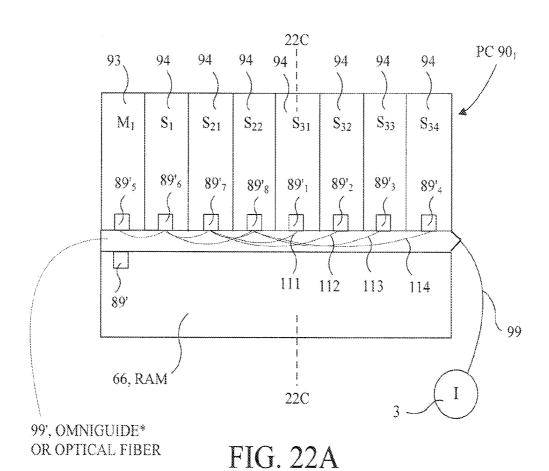

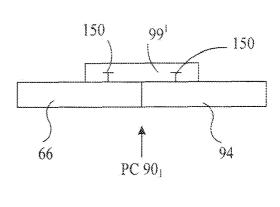

FIGS. 21A and 21B are similar to FIGS. 20A and 20B, but puter or personal computer on a microchip can have a separate input/output communication link to a digital signal processor (DSP) or other transmission/reception connection component. FIG. 21C shows a H-tree configuration of binary tree networks.

FIGS. 22A-22C show a PC microprocessor on a microchip similar to that of FIG. 21B, except that FIG. 22A shows microprocessors 93 and 94 each connecting to an optical wired connection 99' such as thin mirrored hollow wire or optical omniguide or optical fiber.

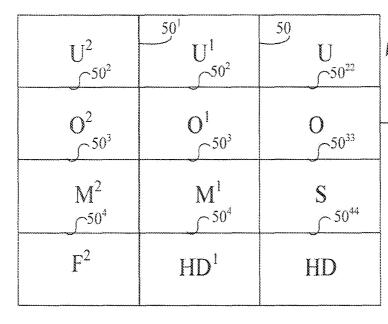

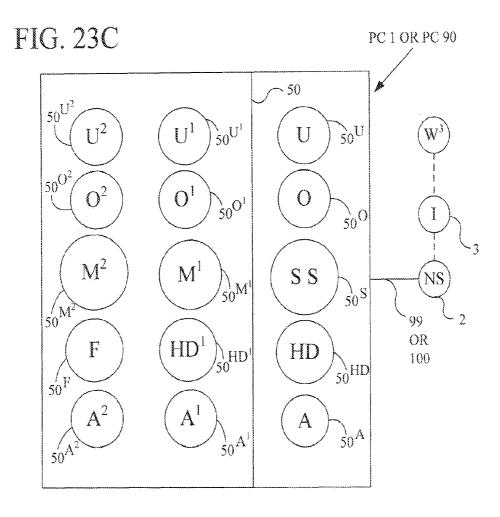

FIGS. 23A-23E show multiple firewalls 50 within a personal computer 1 or PC microchip 90.

FIG. 24 shows a hard drive with an internal firewall 50.

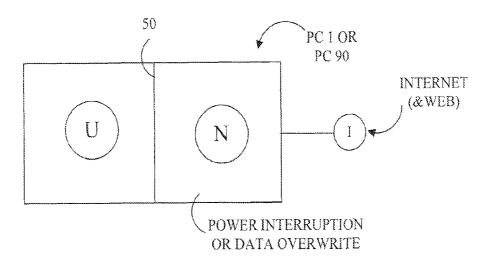

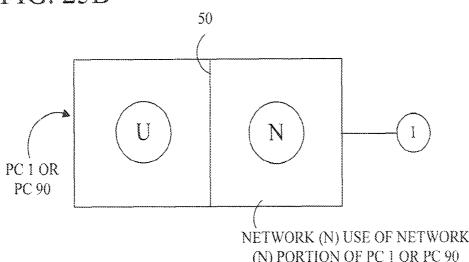

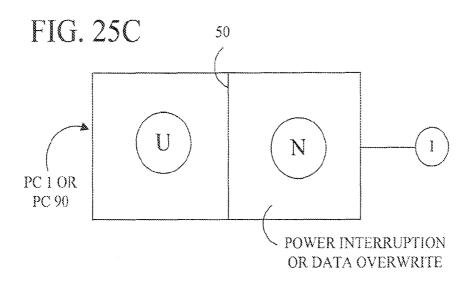

FIGS. 25A-25D show the use for security of power interruption or data overwrite of volatile memory like DRAM and  $\,^{40}$ non-volatile memory like Flash or MRAM (or ovonics), respectively, of the network portion of a personal computer PC1 or system on a microchip PC90.

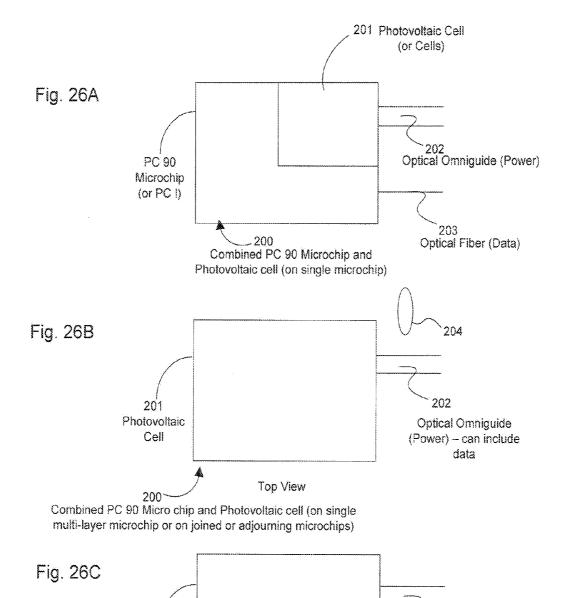

FIGS. 26A-26C show exemplary microchip and photovoltaic cell embodiments.

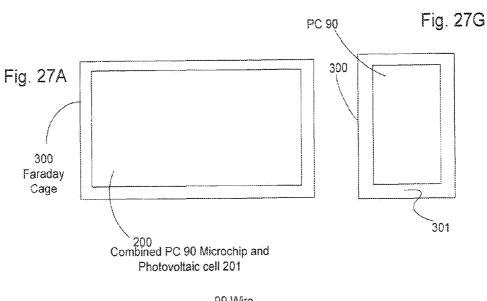

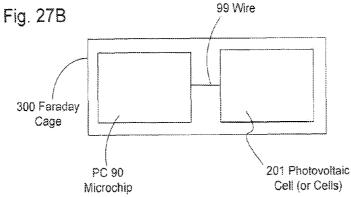

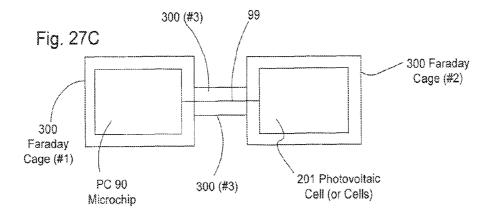

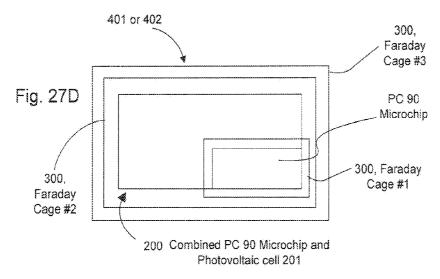

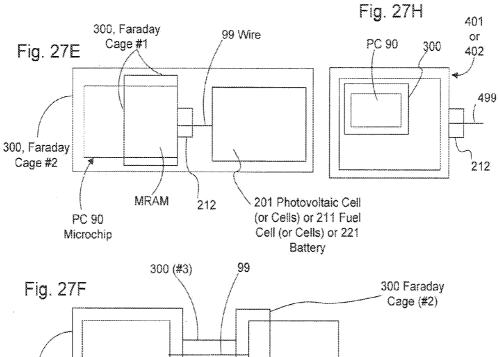

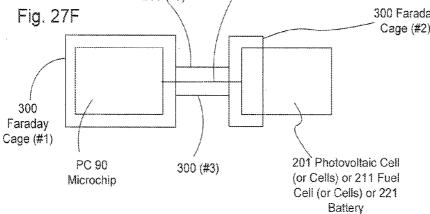

FIGS. 27A-27H show exemplary microchip and Faraday Cage embodiments.

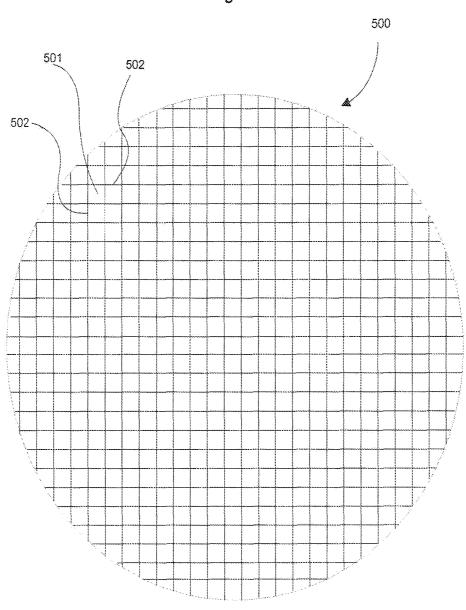

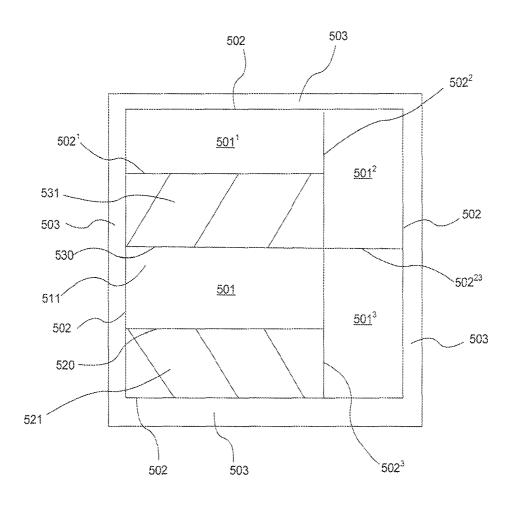

FIG. 28 shows a silicon wafer 500 used to make microchips.

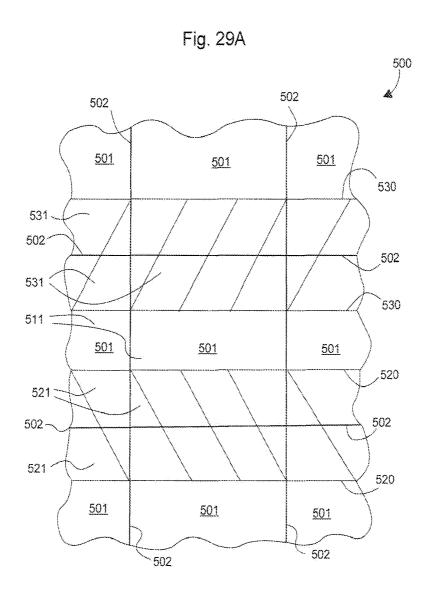

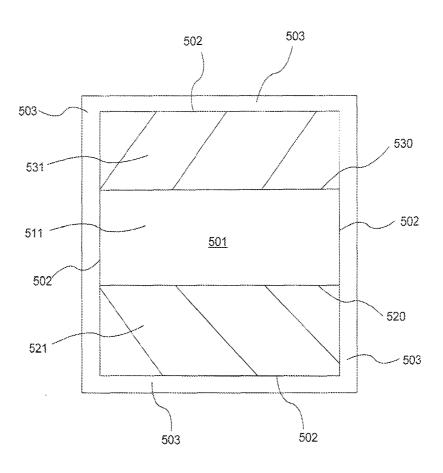

FIG. 29A shows a top view of a microchip 501 surrounded 50 by adjoining portions of adjoining microchips 501 in a section of the silicon wafer 500. FIG. 29B shows a top view of the microchip 501 embodiment of FIG. 29A after the die has been separated from the silicon wafer 500 and positioned in a microchip package 503.

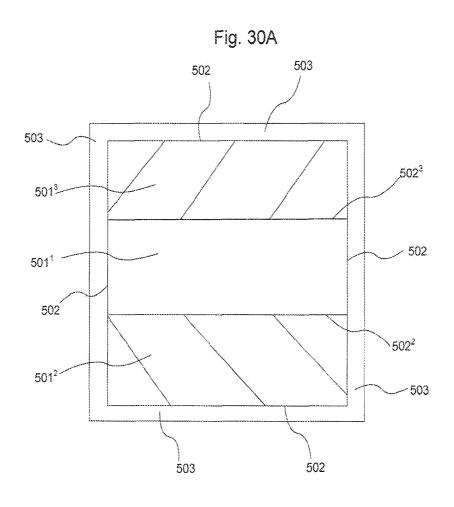

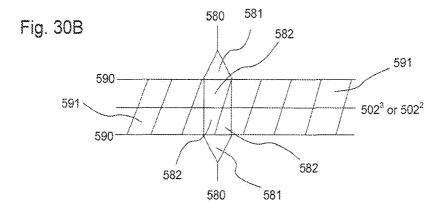

FIGS. 30A-30C show alternative embodiments that unite separate fabrication processes on the same microchip 501.

FIG. 31 shows a combination of the embodiments shown in FIGS. 29 and 30.

# DETAILED DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

Embodiments useful for a network of computers are presented. In an embodiment, an apparatus includes a microchip 65 and a Faraday Cage. The microchip includes a personal computer with a general purpose microprocessor on the micro10

chip. The Faraday Cage surrounds at least a portion of the microchip. In another embodiment, an apparatus includes a microchip. The microchip includes a general purpose microprocessor and one or more photovoltaic cells.

The new network computer utilizes PC's as providers of computing power to the network, not just users of network services. These connections between network and personal computer are enabled by a new form of computer/network financial structure that is rooted in the fact that economic resources being provided the network by PC owners (or leaser) are similar in value to those being provided by the network provider providing connectivity.